|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Методы подавления шумов, помех электронных систем 1 ... 50 51 52 53 54 55 56 ... 59 имеющий 8 информационных -ВЫХОДЬ! налов. Группу передающих вентилей можно использовать для того, чтобы производить выбор одного из нескольких входов (вырабатывая управляющие сигналы с помощью дешифратора, как будет показано ниже). Эта логическая функция настолько широко используется, что получила официальное название мультиплексора , который и будет рассмотрен следующим пунктом. Упражнение 8.16. Покажите, как построить схему выборки на два входа с помощью передающих вентилей. Здесь нужно использовать инвертор. Мультиплексоры. Венгшь выборки на два входа известен также под названием 2-входового мультиплексора. Промышленность выпускает также мультиплексоры на 4, 8 и 16 входов (устройства на 4 входа выпускаются сдвоенными, т. е. по 2 в одном корпусе). Двоичный адрес служит для выбора входа, сигнал с которого должен поступить на выход. Например, мультиплексор, входов, использует для адресации к ним 3-разрядный адресный вход, как показано на рис. 8.31, где представлен цифровой мультиплексор типа 74151. Он имеет стробирую-щий (или разрешающий) вход £, ра- ] ботающнй в отрицательной логике, а также прямой и инверсный выходы. Когда устройство закрыто (на входе Е действует ВЫСОКИЙ уровень), выход Q будет иметь НИЗКИЙ уровень, а Q - ВЫСОКИЙ независимо от состояния адресных и информационных входов. В семействе КМОП имеются два типа мультиплексоров, первый из которых применяется только для работы с цифровыми сигналами. Он имеет входной порог и регенерирует на выходе чистые уровни, которые соответствуют входному состоянию. Таким же образом работают все логические элементы семейства ТТЛ. Примером подобной ИМС является также сдвоенный 4-входовый мультиплексор КМОП 4539, который представляет собой полный аналог ТТЛ-мультиплексора 74153. К другому типу относятся аналоговые двунаправленные КМОП-мультиплексоры, которые фактически представляют собой ряд передающих вентилей, К подобным устройствам относятся КМОП-муль-типлексоры 4051-4053. Поскольку передающие вентили являются двунаправленными, эти мультиплексоры могут использоваться в качестве демультиплексоров или дешифраторов, которые и будут рассмотрены в следующем разделе. Упражнение 8.17. Покажите, как с помощью вентилей построить мультиплексор а 4 входа.

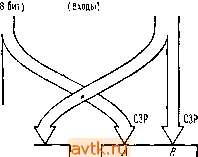

Рио. 8,31. При разработке логических устройств может потребоваться производить выбор из большего числа входов, чем имеется в мультиплексоре. Этот вопрос относится к обш,ей задаче расширения (или нара-щ,нвания) И*С, которое заключается в использовании нескольких -В, i 75 LSI 51  Рис, 8,32. Наращивание мультиплексора. ИМС с небольшими индивидуальными возможностями для получения схемы с большими возможностями, и применяется к дешифраторам, памяти, регистрам сдвига, арифметически-логическим и другим устройствам. Как видно из рис. 8.32, в данном случае наращивание выполняется очень просто. Здесь показано, как с помощью двух мультиплексоров на 8 входов типа 74LS161 строится мультиплексор на 16 входов. В схеме имеется дополнительный адресный разряд, с помощью которого отключается одна или другая ИМС. На выходе Q отключенной схемы поддерживается НИЗКИЙ уровень, что позволяет производить наращивание с помощью вентиля ИЛИ. Если выходы имеют три состояния, Дзоиччо^ то наращивание производится еще десятичт 2 71:342 проще: для этого достаточно непо- средственно объединить выходы. HtHHH! Демулыпиплексоры адеша- Десй1,1 ньи mm фраторы. Лещлътиплекс op при-  Рис. 8.33. нимает входной сигнал и направляет его на один из нескольких выходов в соответствии с двоичным кодом, действующим на адресных входах. Остальные выходы в этом случае находятся либо в неактивном состоянии, либо в состоянии разомкнутой цепи. Аналогично работает и дешифратор, единственное отличие которого состоит в том, что на входы подается только адрес, возбуждающий один из п возможных выходов. На рис. 8.33 показан дешифратор типа 7442, выполняющий преобразование двоичгюго кода в десятичный. Выход, который соответствует действующему на входе двоично-десятичному коду, имеет НИЗКИЙ уровень, а остальные - ВЫСОКИЙ. Эта схема, в частности, может применяться для управления цифровым индикатором или для определения состояний счетчика. В семействе КМОП в качестве демультиплексоров могут работать мультиплексоры, использующие передающие вентили, так как последние являются двунаправленными. В этом случае необходимо помнить о том, что невозбужденные выходы ведут себя как разомкнутая цепь. Для того чтобы на этих выходах действовали нужные логические уровни, следует использовать нагрузочный резистор или его эквивалент (те же требования, что и для вентилей ТТЛ с открытым коллектором). Существует другой тип дешифраторов, который обычно входит в состав всех логических семейств. Примером такого дешифратора является преобразователь двоично-десятичного кода в семисегментный с формирователями для управления цифровым индикатором 7447 . Эта схема в соответствии с двоично-десятичным кодом, действующим на входе, формирует сигналы на всех выходных линиях, связанных о входами семисегментного цифрового индикатора, воспроизводящего десятичный символ. Устройство такого типа фактически является кодопреобразователем, но в обычной практике носит название дешифратора. Упражнение 8.18. Используя вентили, постройте преобразователь двоично-де< сятичного кода в десятичный. Приоритетный шифратор. Приоритетный шифратор формиру* ет на выходе двоичный код, соответствующий возбужденному входу о наибольшим номером. Наиболее часто эта схема используется в аналого-цифровых преобразователях (АЦП) (см. следующую главу) и в микропроцессорных системах. Примерами стандартных ИМС такого типа являются 8-входовые (3 выходных разряда) приоритетные шифраторы КМОП 4532 и ТТЛ 74148. Упражнение 8.19. Постройте Вход А Вход В простейший шифратор, 2-разрядный адрес на выходе которого будет указывать, какой из четырех входов ичеет ВЫСОКИЙ уровень (все m/f.fi должны иметь Вход - /Tg. ЖЪЪЪ Лвмк - Bbixoif пикии уровень). переноса перенос Сумматоры и другие ПМС для выполнения (Арифметических функций. На рис. 8.34 показан 4- Рис 8.34, разрядный полный сумматор. Он прибавляет 4-разрядное двоичное число At к 4-разрядному числу о< и вырабатывает на выходе 4-разрядную сумму S, плюс разряд переноса Явых. Для суммирования больших величин сумматоры можно Наращивать. Для этой цели предусмотрен вход переноса П^, на кото-  Глаеа SI рый поступает выходной сигнал переноса от предыдущего (младшего) сумматора. На рис. 8.35 показано, как строится схема для суммирова-ния двух 8-разрядных двоичных чисел. В качестве сумматора часто используются арифметически-логические устройства (АЛУ). Эти устройства фактически предназначены для выполнения целого ряда различных функций. В частности, я (8 бит)  МЗР МЗР А В 5,---- МЗР 74L583 /7выкН 5,----4 СЗР Э-разрядная сумма (выход) Рис. 8.35. 4-разрядное АЛУ типа 74181 (с возможностью наращивания для обработки слов большей длины) может выполнять сложение, вычитание, сдвиг двоичных разрядов, сравнение величин и некоторые другие функции. Время выполнения арифметических операций в сумматорах и АЛУ лежит в пределах от нескольких десятков наносекунд (для ТТЛ) до нескольких сотен наносекунд (для КМОП). В настоящее время выпускаются ИМС умножителей, имеющие две конфигурации: 8 бит х 8 бит и 16 бит X 16 бит. Пока они еще доста- ВхоД А Вход В Входы для наращивания 1 I I Г 1 I I 1

точно дороги, но имеют очень хорошие характеристики. Типичное значение для времени выполнения умножения 16x16 составляет величину порядка 100 НС. Рис 8 36 (Должно быть Во ... Вз - Прим ред ) Компараторы. На рис. 8.36 показан 4-разрядный компаратор чисел. Он определяет относительные значения чисел Л и S и вырабатывает на выходе сигналы, соответствующие соотноше- ниям А < В, Л =В и А> В. Входы допускают наращивание для обработки чисел длиной более 4 бит. Упражнение 8.20. Используя вентили Исключающее ИЛИ , постройте компаратор для 4-разрядных величин Л и 5, который будет определять, справедливо ли соотношение А=В. Схема формирования и контроля паритета. Это устройство предназначено для выработки паритетного бита, который добавляется к информационному слову при передаче (или записи) данных, а также для проверки правильности паритета при восстановлении этих данных. Паритет может быть четным или нечетным (при нечетном паритете для каждого символа общее число битов (разрядов), содержащих 1, нечетно). Например, формирователь паритета типа 74180 принимает 8-разрядное входное слово и в соответствии с состоянием управляющего входа вырабатывает на выходе четный или нечетный бит. Конструктивно схема представляет собой набор вентилей Исключающее ИЛИ . Упражнение 8.21. Подумайте, как сделать формирователь паритета с помощью вентилей Исключающее ИЛИ . Некоторые другие функциональные ИМС. Существует также большое число других не упоминавшихся ранее комбинационных БИС, которые представляют несомненный интерес. Например, в семействе КМОП есть мажоритарный узел , который сигнализирует о том, что возбуждена большая часть его входов. Имеется также двоично-десятичное устройство дополнения до 9 , назначение которого не требует пояснений. Фирма Signetics выпускает кристалл ТТЛ под номером 8243, который представляет собой табулятор битовых позиций . Это устройство производит сдвиг 8-разрядного входного кода на заданное число битов и может наращиваться до любой длины. В дальнейшем выбор нестандартных функциональных ИМС будет становиться еще шире, поскольку постоянно возникают задачи, которые требуют своего решения. 8.15. Реализация произвольных логических функций, заданных с помощью таблиц истинности При достаточно сложной таблице истинности соответствующая ей вентильная схема может оказаться слишком громоздкой. Здесь естественно возникает вопрос, нельзя ли найти какой-то другой путь. Таких путей существует несколько. В данном разделе мы рассмотрим применение мультиплексоров и демультиплексоров для реализации произвольных таблиц истинности, а затем вкратце расскажем о ПЗУ и программируемых логических матрицах (ПЛМ), последних из класса Комбинационных функциональных ИМС. Мультиплексоры в качестве реализаций обобщенных паблиц истинности. Нетрудно понять, что мультиплексор на п входов может быть использован для генерации любой таблицы истинности СЗР па п входов без применения каких-либо внешних компонентов, если на соответствующие входы подать ВЫСОКИЕ или НИЗКИЕ уровни. На рис. 8.37 показана схема, которая определяет, является ли важным код, действующий на ее 3-разрядном входе. Не столь очевидным является тот факт, что мультиплексор на п входов с помощью лишь одного внешнего инвертора может быть использован для генерации таблицы истинности, имеющей 2п входов. Дело ~ заключается в следующем. Рис. 8.37. (Должно быть До... л. Прим.ред) Сначала составляется таблица истинности для всех перестановок по п - 1 бит. Для каждой такой перестановки выходной сигнал можно определить по состоянию п-го бита одним из четырех возможных способов:

Q (Di, Di, QiDy, Di,

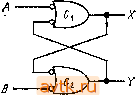

Затем функция D подается на вход, адресуемый с помощью сигналов Du Di, .. ., D i. Для иллюстрации построим схему, которая позволяет узнать, содержит ли заданный месяц года 31 день. р. , L i , Каждый месяц определяется - г- 4-разрядным двоичным кодом. Сначала составим таблицу истинности (табл. 8.4), после чего останется лишь прочитать значения сигналов для соответствующих входов мультиплексора и посмотреть, как Q зависит от четвертого входного бита Ло. На рис. 8.38 показана схемная реализация такого устройства, в которой использован КМОП-мультиплексор на 8 входов типа 4051. В общем случае на индивидуальные входы может быть подан высокий уровень, НИЗКИЙ уровень, D или D. Упражнение 8.22. Убедитесь, что эта схема действительно сообщает о том, имеет ли заданный месяц 31 день. Забавное примечание: оказывается, эту таблицу истинности можно реализовать при помощи одного вентиля Исключающее ИЛИ , если использовать для несуществующих месяцев знак X (любое значение). Рис. 8.38. Логическое вычисление количества дней в месяце

Попробуйте сделать это самостоятельно. Такая работа даст вам возможность приобрести опыт в составлении карт Карно. Дешифраторы как обобщенные таблицы истинности. Использование дешифраторов также позволяет упростить комбинационную логику, особенно в тех случаях, когда нужно получить несколько одновременно действующих выходных сигналов. В качестве примера попробуем составить схему преобразования двоично-десятичного кода в код с избытком 3. Таблица истинности для такого преобразования имеет вид:

Здесь 4-разрядиый двоично-десятичный вход используется для задания адресов дешифратору, а выходы дешифратора (в отрицательной логике) служат в качестве входов для нескольких вентилей ИЛИ, формирующих выходные биты (рис. 8.39). Заметим, что в данной схеме выходные биты не являются взаимно исключающими. Аналогичная схема может [ двоично-десятичный korI А В С Л 7Ш 0 15455 с- 7 8 9  Рис. 8.39. Кодовое преобразование на уровне мини-термов: преобразователь двоично-десятичиого кода в код с избытком 3. быть использована в качестве устройства для задания рабочих циклов в стиральной машине: при каждом состоянии входа выполняются различные функции (подача воды, заполнение, вращение барабана и т. д.). Вскоре вы увидите, каким образом вырабатывается последовательность двоичных кодов, следующих через равные интервалы времени. Индивидуальные выходы дешифратора носят название мини-термы и соответствуют позициям на карте Карно. Постоянное запоминающее устройство (ПЗУ) фактически представляет собой устройство с памятью и подробно будет рассматриваться позднее, вместе с триггерами, регистрами и т. п. Характерная особенность ПЗУ состоит в том, что оно постоянно запрограммировано на определенную комбинацию бит и сохраняет эту информацию даже при отключении питания. Например, ПЗУ 32x8 для каждого из 32 входных состояний, определяемых 5-разрядным адресом, вырабатывает 8 выходных бит. Таким образом, при помощи ПЗУ можно запрограммировать любую комбинационную таблицу истинности. Умножитель 2x2 из упражнения 8.14 может, например, быть реализован с помощью одного программируемого ПЗУ типа 74188 прп использовании 4 из 5 входных адресных линий и 4 из 8 выходных информационных линий. Промышленностью выпускаются ПЗУ различных конфигураций, начиная от небольших устройств с объемом 1024x4 (4 выходных бита для каждого 10-разрядного адреса) и кончая большими ЗУ объемом 8 Кх8. Более подробно ПЗУ будут описанЬ! в гл. 11. В соответствии со способом программирования ПЗУ подразделяются на несколько типов, В масочно-программируемых ПЗУ комбинация их битов задается при изготовлении. Перепрограммируемые ПЗУ (ППЗУ) программируются пользователем. После этого записанная в них комбинация бит сохраняется постоянной. Программируемые ПЗУ со стиранием позволяют стирать, когда это требуется, записанную в них информацию (стирание осуществляется с помощью интенсивного ультрафиолетового излучения, которое подается через прозрачное кварцевое окошко, расположенное в корпусе ПЗУ). Электрически программируемые ПЗУ (ЭППЗУ) стираются электрическим путем, будучи установленными в схему. ПЗУ находят широкое применение в ЭВМ и микропроцессорах, где они используются для хранения законченных программ. Однако следует помнить и о том, что ПЗУ меньших объемов позволяют заменить собой громоздкие наборы вентилей. Другое устройство, о котором следует также знать тем, кто собирается строить сложные узлы с комбинационной логикой, представляет собой программируемую логическую матрицу (ПЛМ). Эти микросхемы содержат большое число вентилей, которые можно соединять между собой таким образом, чтобы они выполняли требуемые лбгические функции. ПЛМ могут быть масочно-программируемые и программируемые током. Программирование первых производится при изготовлении в соответствии с требованиями пользователя. Вторые программируются пользователем путем выжигания внутренних связей, существующих между вентилями исходной матрицы. Примером ПЛМ, программируемой током, является устройство 82S100, которое может формировать о выходных сигналов, определяемых логической комбинацией 16 входов. Ту же самую функцию выполняет масочно-программируемый вариант ПЛМ 82S200.  ПОСЛЕДОВАТЕЛЬНАЯ ЛОГИКА 8.16. Устройства с памятью: триггеры Вся рассмотренная выше цифровая логика строилась на комбинационных схемах, наборах вентилей, в которых выход полностью определяется текущим состоянием входов. В этих схемах отсутствует память , отсутствует предыстория. Цифровая логика станет намного более интересной, если эти устройства снабдить памятью. Тогда с их помощью можно будет строить счетчики, арифметические регистры и различные умные схемы, которые, выполнив одну интересную функцию, начинают делать другую. Основным узлом таких схем является триггер, представленный в простейшей форме на рис. 8.40. Рис. 8.40, Предположим, что оба входа А и В имеют высокий уровень, в каком состоянии будут выходы X и У? Если X имеет ВЫСОКИЙ уровень, то последний будет присутствовать на обоих входах Сг, устанавливая Y в состояние НИЗКОГО уровня.Это согласуется с состоянием выходаХ (ВЫСОКИЙ уровень), следовательно, все правильно. Не так ли? X = S, Y = H. Неверно! Схема симметрична, следовательно, правомерно будет и состояние, при котором Состояние, когда оба выхода X и У имеют ВЫСОКИЙ (или НИЗКИЙ) уровень, невозможно (вспомним, что А=В=В). Таким образо.м, триггер имеет два устойчивых состояния (иногда его называют биста-бильной схемой). В котором из этих двух состояний он окажется, зависит от его предыстории, т. е. он имеет память. Для того чтобы в эту память что-то записать, достаточно на один из входов триггера кратковременно подать НИЗКИЙ уровень. Например, после кратковременной подачи НИЗКОГО уровня на вход А триггер гарантированно установится в состояние Х=Б, Y = H независимо от того, какое состояние он имел прежде. Подавление дребезга контактов. Рассмотренный нами тип триггера со входами S (установки в 1 ) и R (установки в О или сброса) оказывается весьма полезным для многих применений. Типичный пример его использования показан на рис. 8.41. По замыслу эта схема должна открывать вентиль и пропускать входные импульсы, если ключ разомкнут. Ключ подключен к земле, а не к шине +5 В, поскольку в состоянии НИЗКОГО уровня требуется отвод тока от входа ТТЛ,- в 1 ... 50 51 52 53 54 55 56 ... 59 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |