|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Методы подавления шумов, помех электронных систем 1 ... 51 52 53 54 55 56 57 ... 59 то время как в состоянии ВЫСОКОГО уровня нужно лишь преодолеть ток утечки (для стандартных ТТЛ 40 мкА, макс). Кроме того, обычно в устройствах имеется шина земли, удобная для подключения к ней ключей и других органов управления. При использовании такой схемы возникает проблема, связанная с дребезгом контакта ключа. В течение 1,0 кОм лп \ интервала порядка 1 мс после замыкания ключа его контакты входят в соприкосновение друг с другом обычно от 10 до 100 раз. В результате форма сигнала имеет вид, показанный на рис. 8.41. Если к выходу такой схемы подключить счетчик или регистр сдвига, то они наверняка отреагируют на каждый дополнительный импульс, вызванный этим дребезгом контактов. На рис. 8.42 показано, как решается эта проблема. При первом же соприкосновении контактов триггер изменит свое состояние и в дальнейшем уже не будет реагировать на последующий дребезг, поскольку двухпозиционный однополюсный ключ не может совершать колебаний до противоположной позиции. В результате дребезг выходного сигнала будет отсутствовать, как и показано на диаграмме. Такая схема находит широкое применение и выпускается в виде стандартной ИМС National М8544 ( счетверенный подавитель дребезга , имеющий внутренние резисторы и выходные каскады с тремя состояниями). К сожалению, такая схема имеет небольшой недостаток. Дело в том, что первый импульс, возникающий на выходе вентиля после того, как он откроется, может оказаться укороченным: это определяется моментом замыкания ключа по отношению к входной серии импульсов. То же самое относится и к конечному импульсу последовательности (разумеется, все это свойст- венно также и ключам без подавления дребезга). В тех случаях, когда этот нежелательный эффект может иметь значение, применяется схема синхронизатора, которая позволяет его устранить.  Рис. 8.42. СБРОС ОБЩИЙ П. Сброс СШИБКА ЛВАРИЯ Рис. 8.43.  Многовходовые триггеры. На рис. 8.43 показана еще одна простая схема триггера. В ней использованы вентили ИЛИ-НЕ: ВЫСОКИЙ уровень на входе устанавливает соответствующий выход триггера в состояние НИЗКОГО уровня. Наличие нескольких входов дает возможность устанавливать триггер в 1 и О различными сигналами. В схеме, показанной на рисунке, резисторы для подпитки входов не используются, поскольку входные сигналы поступают от логических элементов устройства (имеющих стандартные выходы с активной нагрузкой). 8.17. Тактируемые триггеры Триггеры, построенные на двух вентилях, как показано на рис. 8.43, обычно называют RS (от английских слов set - установка и reset - сброс ) или асинхронными триггерами. Путем подачи соответствующе-го входного сигнала они могут быть установлены в то или иное состояние. /?5-триггеры удобно использовать в схемах защиты от дребезга контактов, а также во многих других случаях, однако более широкое применение получили триггеры, схема которых несколько отличается от рассмотренной. Вместо пары асинхронных входов они имеют один или два информационных входа и один тактирующий. В момент подачи тактирующего импульса выходное состояние триггера может либо измениться, либо остаться прежним, в зависимости от того, какие сигналы действуют по информационным входам. Простейшая схема тактируемого триггера приведена на рис. 8.44. От рассмотренной выше она отличается наличием двух вентилей (управляемых тактовыми сигналами), которые отпирают входы установки в О и 1 . Легко проверить, что таблица истинности для этого триггера б)дет иметь вид  Рйс. 8.44.

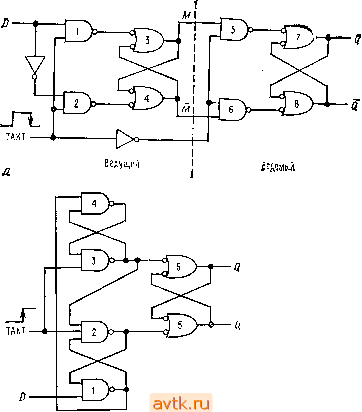

где -состояние выхода- Q после подачи {п + 1)-го тактового импульса, а Qn - до его поступления. Главное отлпчие этой схемы ог предыдущей состоит в том, что входы S п R здесь должны рассматриваться как информационные и сигналы, присутствующие на этих входах в момент поступления тактового импульса, определяют, что произойдет с выходом Q.  Срабатывание по поломтельном перепаду Рис. 8.45. £)-триггеры, работающие по фронту. Этот триггер имеет один недостаток. Дело в том, что изменение выходного состояния в соответствии со входными сигналами может происходить в течение всего интервала времени, на котором тактовый импульс имеет ВЫСОКИЙ уровень. В этом смысле он еще подобен асинхронному i?S-Tpnrrepy. (Схема эта известна также под названием прозрачный фиксатор , поскольку выход насквозь просматривает ход в течение интервала действия тактового сигнала.) Всесторонние Р Рис. 8.46.  ВОЗМОЖНОСТИ триггерных схем раскроются после введения новых, несколько отличных от рассмотренных конфигураций, которые представляют собой триггер типа ведущий-ведомый (двухступенчатый) и триггер, работающий по фронту. Триггеры типа ведущий-ведомый и триггеры.работающие по фронту. Эти типы триггеров являются наиболее распространенными. Информация, поступившая на входные линии этого триггера к моменту возникновения перепада или фронта тактового сигнала, определяет, каким будет состояние выхода на последующем интервале времени. Такие триггеры выпускаются в виде недорогих ИМС и всегда используются в этом виде, однако, для того чтобы понять, как они работают, имеет смысл рассмотреть их внутреннюю структуру. На I I рис. 8.45 показаны принцнпи- ~ альные схемы так называемых D-триггеров. Информация, поступившая на D-вход, будет передана на выход Q после подачи тактового импульса. Рассмотрим принцип действия триггера типа ведущий-ведомый (рис. 8.45, а). Когда тактовый сигнал имеет ВЫСОКИЙ уровень, разрешается работа вентилей I и 2, через которые ведущий триггер (вентили 3 и 4) устанавливается в состояние, соответствующее D-входу: M=D, M=D. Вентили 5 и 6 закрыты, поэтому ведомый триггер (вентили 7 и 8) сохраняет свое предыдущее состояние. Когда тактовый сигнал перейдет в состояние НИЗКОГО уровня, входы ведущего триггера отключатся отО-входа, а входы ведомого подключатся к выходу ведущего, в результате чего последний передаст свое состояние ведомому триггеру. После этого никакие изменения на выходе произойти не смогут, поскольку ведущий триггер заблокирован. С приходом следующего тактового сигнала ведомый триггер отключится от ведущего, а ведущий воспримет новое состояние входа. С точки зрения внешних сигналов триггер, работающий по фронту, ведет себя точно так же, однако внутри он работает по-другому. Принцип его действия нетрудно разобрать самостоятельно. Показанная на рис. 8.45, б схема представляет собой распространенный D-триггер семейства ТТЛ, срабатывающий на положительном перепаде. В рассмотренном ранее триггере типа ведущий-ведомый данные на выход передаются по отрицательному перепаду тактового импульса. В номенклатуру стандартных ИМС, выпускаемых промышленностью, входят триггеры, срабатывающие как по одной, так и по другой полярности перепада. Кроме того, большинство триггеров имеет также асинхронные входы S и /?. В зависимости от типа установка триггера в 1 и Ю по этим входам может производиться как ВЫСОКИМ, так и НИЗ- КИМ уровнем. На рис. 8.46 показано несколько наиболее распространенных триггерных ИМС. Стрелка означает динамический вход (срабатывание по фронту), а кружок - инверсию Таким образом, изображенная на рисунке схема ТТЛ 7474 представляет собой сдвоенный D-триггер, срабатывающий по положительному перепаду и имеющий асинхронные входы S н R, активные по НИЗКОМУ уровню. Схема 1013 представляет собой сдвоенный 0-триггер семейства КМОП, срабатывающий по положительному перепаду и имеющий асинхронные входы S и активные по ВЫСОКОМУ уровню. Интегральная схема 7473 - это сдвоенный У/С-триггер типа ведущий-ведомый , который срабатывает по отрицательному перепаду и имеет вход сброса, активный по НИЗКОМУ уровню. JK-траггер. По принципу работы У/С-триггер аналогиченD-триг-геру, но имеет два информационных входа. Приведем таблицу истинности для J/C-триггера:

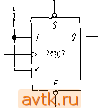

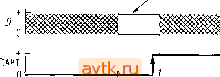

Если на входах J \\ К действуют противоположные сигналы, то на очередном фронте тактового импульса выход Q воспроизведет значение У-входа. Если оба входа J и К имеют НИЗКИЙ уровень, то состояние выхода не изменится. И наконец, если на обоих входах действует ВЫСОКИЙ уровень, триггер будет совершать скачки (менять свое состояние на каждом тактовом импульсе), т. е. работать в счетном режиме. Предупреждение. Некоторые старые типы J/C-триггеров представляют собой ловушку для единиц - термин, который вы не найдете ни в одной документации, но означающий явление, которое может привести неосведомленного человека к весьма неприятным последствиям. Дело в том, что если на интервале, когда ведомый триггер открыт тактовым сигналом, вход J или К (или оба одновременно) на какой-то Момент изменит свое состояние, а затем до окончания тактового сигнала вернется в исходное, то это кратковременное состояние будет запомнено триггером и в дальнейшем он будет вести себя так, как если бы это состояние сохранилось. В результате триггер может переброситься на следующем тактовом перепаде, даже если сигналы, действующие в момент этого перепада на входах J и К, подтверждают предыдущее состояние. Это может привести, мягко говоря, к своеобразному поведению. Проблема возникает вследствие того,что эти триггеры были Глет 8 сконструированы в предположении, что тактовый импульс имеет очень короткую длительность, в то время как в действительности тактирование всегда производится сигналом конечной длительности, При использовании триггеров типа ведущий-ведомый следует соблюдать меры предосторожности либо вообще избегать их, применяя более надежные триггеры, работающие по фронту. Делатель на 2. Используя способность триггеров работать в счетном режиме, легко построить схему делителя на 2, два способа  0 Q > mi Выход Рис. 8.47, построения которого показаны на рис. 8.47. Когда оба входа имеют ВЫСОКИЙ уровень, (-триггер совершает скачки и вырабатывает выходной сигнал, показанный на рисунке. Вторая схема также будет совершать перебросы, поскольку ее D-вход подключен к собственному выходу Q и в момент поступления тактового импульса на D-входе всегда действует инверсия по отношению к текущему состоянию триггера. В любом случае частота сигнала на выходе будет равна половине входной частоты. Синхронизация информации и тактов. В связи с последней схемой возникает интересный вопрос: не получится ли так, что триггер не сможет переброситься, поскольку состояние D-входа изменяется почти сразу же вслед за тактовым импульсом? Иными словами, не начнет ли схема сбиваться, если на ее входе происходят такие странные явления? Этот вопрос можно сформулировать и следующим образом: в какой точно момент по отношению к тактовому импульсу D-триггер (или какой-либо другой) анализирует состояние своего входа? Ответ состоит в том, что для любого тактируемого устпойства с ществует ус г Информация может изменяться Информация Информация меняться может и? должна изменяться  20 нс мин. -Н Н-уц 5 чс мин. Рис. 8.48. Времена установления данных и удержания. определенное время установления / и время удержания /уд. Для того чтобы схема работала правильно, информация должна поступать на вход не позднее чем за время /уе. до возникновения тактового перепада и оставаться неизменной по крайней мере в течение / после него. Например, для триггера 7474 / =20 не, а /уд=5 не (рис. 8.48). В рассмотренной схеме счетного триггера требование к времени установления будет удовлетворено в том случае, если состояние выхода сохраняется неизменным в течение, как минимум, 20 НС, предшествующих очередному тактовому перепаду. Может показаться, что при этом нарушается требование к времени удержания, однако это не гак. Минимальное время распространения сигнала с тактового входа на выход составляет 10 не, и D-триггер, включенный в счетном режиме, будет иметь неизменное состояние D-входа в течение гю меньшей мере 10 НС. Большинство современных устройств вообще не предъявляют требований ко времени удержания. Если сигнал на D-входе меняется на интервале времени установления, то может возникнуть любопытный эффект, носящий название метастабильное состояние , при котором триггер не способен определить, в какое состояние ои должен перейти. Об этом явлении мы вскоре еще упомянем. Деление на число, большее чем 2. С помощью каскадного соединения нескольких счешых триггеров (выход Q каждого предыдущего триггера подключен к тактовому входу последующего) легко получить делитель на 2 , или двоичный счетчик. На рис. 8.49 показана схема четырехразрядного асинхронного счетчика и даны его временные диаграммы. Заметим, что если выход Q каждого триггера непосредственно действует на тактовый вход следующего, срабатывание триггеров должно происходить по спаду (заднему фронту) сигнала на тактовом входе (показано кружком инверсии). Схема, показанная на рисунке, представляет собой счетчик-делитель на 16: на выходе последнего триггера формируются прямоугольные импульсы, следующие с частотой, равной Vt, частоты входного тактового сигнала. Схема называется счетчиком, поскольку информация, присутствующая на четырех выходах Q, может рассматриваться как 4-разрядное двоичное число, которое изменяется от О до 15, увеличиваясь на единицу с каждым входным импульсом. Этот факт отражает временная диаграмма на рис. 8.49, на которой СЗР означает старший значащий разряд , МЗР - младший значащий разряд , а изогнутые стрелки, служащие Глаеа 8 для облегчения понимания, указывают, какими перепадами вызываются изменения сигналов. Как вы увидите в разд. 8.25, этот счетчик выполняет настолько важную функцию, что выпускается в виде большого числа модификаций, выполненных в виде однокристальных ИМС, которые могут производить счет в 4-разрядном, двоично-десятичном и многоцифровом бхоаные тзитовые импчльсы а МЗР J Q 1 <к> 1 Ф Л СЗР - < > - к Входные г тактовые А импульсы  (СЗР) о. Состояние Или отсчитанное значение 6 Рис. 8.49. 4-разрядный счетчик: а - принципиальная cxewa; б - врегуеинан диаграмма форматах. Соединяя эти счетчики каскадно и воспроизводя их содержи мое с помощью цифрового индикатора (например, светодиодного), можно легко построить схему для подсчета каких-либо событий Если разрешать прохождение импульсов на вход счетчика в течение ровно 1 с, то получится счетчик частоты, который будет воспроизводить значение частоты путем подсчета числа периодов в секунду. В разд. 14.10 приводятся схемы этого простого, но очень полезного устройства. Промышленность выпускает ИМС счетчиков, в состав которых дополнительно входит генератор, а также схемы управления и вывода на индикацию. Пример такого устройства показан на рис. 8.65. Следует отметить, что эта простейшая схема каскадного счетчика, полученная путем соединения выхода Q каждого триггера с тактовым входом следующей ступени, имеет один недостаток, который связан с покаскадной задержкой распространения сигнала по цепочке триггеров. По этой причине л\чще использовать схему, в которой один и тот же тактовый сигнал подается одновременно на все входы. В следующем разделе мы и перейдем к рассмотрению этих синхронных тактируемых систем. ехофые уроени  Выходные 8.18. Последовательная логика - объединение памяти с вентилями После того как мы изучили свойства триггеров, посмотрим, что можно получить, объединив их с рассмотренной ранее комбинационной (вентильной) логикой. Схемы, составленные из вентилей и триггеров, представляют собой наиболее общую форму цифровой логики. Синхронные тактируемые системы. Мы уже упомянули в предыдущем разделе, что последовательные логические схемы, в которых для управления всеми триггерами используется общий источник тактовых импульсов, обладают рядом преимуществ. В таких синхронных системах все действия происходят сразу же после возникновения тактового импульса и определяются тем состоянием, которое имело место непосредственно перед его возникновением. Общая структура подобной системы показана на рис. 8.50. Все триггеры объединены в один общий регистр, представляющий собой не что иное, как набор D-триггеров, у которых соединены вместе тактовые входы, а индивидуальные D-входы и выходы Q выведены вовне. Каждый тактовый и^:пyльc вызывает передачу уровней, присутствующих на D-входах, на соответствующие выходы Q. Блок, состоящий из вентилей, анализирует состояние выходов регистра и внешних входов, вырабатывая новую комбинацию сигналов для D-входов регистра и выходные логические уровни. Эта простая с виду схема обладает очень большими возможностями. Рассмотрим пример. Пример: деление на 3. Попробуем построить схему синхронного делителя на 3 с помощью двух £)-триггеров, тактируемых входным сигналом. В этом случае Di и Da будут входами регистра, Qi и Qs - его выходами, а общая тактовая линия будет представлять собой главный тактовый вход (рис. 8.51). 18 №804 I III

Рис. 8.50. Классическая последовательная схема: набор регистров памяти, объединенный с комбинационной логикой. 1. Выберем три состояния:

2. Определим, что должно быть на выходах комбинационной схемы, для того чтобы получить последовательность этих состояний, т. е. что Рис. 8.51, должно поступать на D-входы, для того чтобы получить требуемые состояния на выходах: 3. Построим вентильную схему, которая, используя имеющиеся выходы, позволяла бы получить требуемые состояния на входах. В общем л п ги JUUL Рис. 8.52. случае можно использовать карту Карно, однако для данного простого примера можно сразу увидеть, что Di=Qi, 0= (Qi+Qa). чему и соответствует схема на рис. 8.52.  1 ... 51 52 53 54 55 56 57 ... 59 |

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |