|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Классические однокристальные микроконтроллеры 1 ... 6 7 8 9 10 11 12 ... 20 аппаратными средствами, управляющими выбором ведомого (напрщ, мер, дешифратором на адресных линиях). При работе AT89S53 в режиме ведущего данные выводятся чере линию Р1.5. По этой же линии ведомый принимает информацию. Поэтому альтернативная функция Р1.5 носит название MOSI - master data out, slave data in. PI.6 выполняет обратные функции работает на прием у ведущего и на передачу у ведомого. Его наименование - MISO (master data in, slave data out). И наконец, Pi.7 используется для тактирования обмена. Тактовые сигналы вырабатываются ведущим устройством и от него передаются всем ведомым. У ведущего Р1.7 является выходом тактирования, а у ведомых - входом. Подробнее алгоритм работы SPI описывается ниже. AT89S53 имеет аппаратный сторожевой таймер. Будучи разрешенным, он через заданный установками в соответствующем регистре WCON временной промежуток (от 16 до 2048 мс) генерирует сигнал пересброса микроконтроллера. Избежать пересброса можно, если до этого момента сбросить соответствующим сигналом в О содержимое счетчика сторожевого таймера. Обычно для этого разработчики включают в основной цикл программы последовательность команд, обнуляющую счетчик таймера. Зависание программы останавливает выдачу этих команд, и через заданный промежуток времени после этой неприятности контроллер пересбрасывается и вновь начинает нормально функционировать.

Регистровое пространство AT89S53 расширено в сравнении с предшественниками (см. рис. 10). Появились три регистра, обслу-5кивающие SPI - SPCR (0D5H), SPSR (ОААН) и SPDR (086Н). Сторожевой таймер обслуживается регистром WCON (096Н). И наконец, добавлен еще один указатель DPTR (DP1L и DPlH, находящиеся по адресам 084Н и 085Н соответственно). Переключение с основной регистровой пары на дополнительную и обратно осуществляется битом DPS в регистре WCON. Регистры управления SPCR (SPI Control Register) и статуса SPSR (SPI Status Register) описаны в табл. 10 и 11. Таблица 10 Регистр управления SPCR

Рис. 10. Регистровое пространство контроллеров AT89S53 166 Примечание. Значение регистра при сбросе - 000001ХХВ Последовательный периферийный интерфейс предназначен для быстрого синхронного обмена информацией между контроллером и периферией или между двумя контроллерами. Обмен может быть полностью дуплексным и осуществляется, как описа- Регистр статуса SPSR

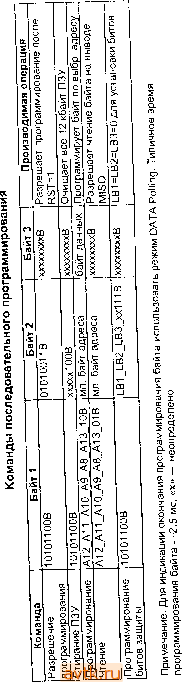

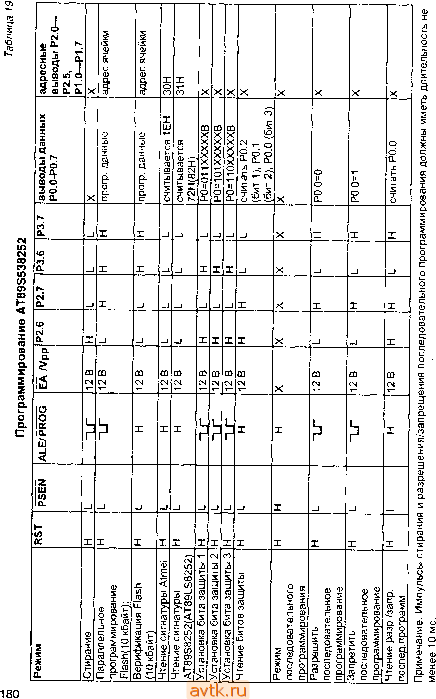

Примечание. Значение регистра при сбросе - ООХХХХХХВ НО выше, с использованием трех линий. Максимальная частота, на которой осуществляется передача, равна четверти частоты осциллятора, т. е. для 24-мегагерцовой версии контроллера она равна 6 МГц. Возможна установка четырех различных скоростей обмена. Передача может осуществляться как младшим битом вперед, так и старшим. Завершение передачи сопровождается установкой в 1 соответствующего флага. На рис. И приведена блок-схема SPI-интерфейса микроконтроллера, а схема соединений узлов SPI двух различных устройств дана на рис. 12. Запись в регистр данных SPI (SPDR) ведущего запускает его тактовый генератор, разрешая прохождение сигналов через делитель частоты. Данные из регистра, бит за битом, поступают на вывод MOSI ведущего, соединенный с одноименным входом ведомого. Каждый импульс тактовой частоты SCK, вырабатываемый ведущим, сопровождается передачей бита. Ведомый принимает бит со своего входа MOSI и заносит его в свой сдвиговый регистр. Одновременно с этим через выход MISO он бит за битом передает ведущему содержимое своего регистра сдвига, который последний принимает по одноименному входу. Таким образом, после прохождения восьми импульсов тактового генератора содержимое сдвиговых регистров ведущего и ведомого обменяется местами. Завершение передачи установит флаг SPIF у ведущего, и при взведенных SPIE и ES вызовет соответствующее прерывание. Если к одному ведущему подключено несколько ведомых, то перед началом обмена первый должен установить в О вход SS (Р1.4) того ведомого, который должен принимать информацию. У невыбранных ведомых при этом и MOSI, и MISO оказываются подключенными к линии как входы, чтобы на линиях не было конфликтов данных. Формат передаваемых данных при различных комбинациях битов СРНА и CPOL приведен на рис. 13, 14. Генератор Делитель на 4/16/64/128 8/16-битный регистр сдвига Буфер чтения Мультиплексор Тактирующие импульсы от ведущего Цепи управления SPI о к о Регистр состояния SPt MSTR Запрос прерывания от SPI Тактирующие импульсы Узел тактирования -I о 0 0 S J М S MISO Р1.6 MOSI PI.5 PI,7 SS P1.4 Регистр управления SPI Внутренняя магистраль данных Рис. 11. Блок-схема SPi-интерфейса микроконтроллера MSB Ведущий LSB MSB Ведомый LSB -- IMISO MIS01 8 - битный регистр сдвига Тактовый генератор SPi MOSI MOSI 8 - битный регистр сдвига Рис. 12. Схема соединений узлов SPI двух различных устройств Регистр управления сторожевым таймером описан в табл. 12. Сторожевой таймер выключен после сброса и в режиме Power Down. Запуск его осуществляется установкой в 1 бита WDTEN, после чего программа должна его периодически сбрасывать, записывая 1 Тактовый цикл SCK (CPOL=0) SCK(CP0L=1)  Рис. 13. Формат передаваемых данных при СРНА=0 Тактовый цикл SCK (CPOL=0) SCK(CP0L=1) MOSI (от ведущего) MISO (от ведомого) SSi (к ведомому) ч  Рис. 14. Формат передаваемых данных при СРНА=1 Таблица 12 JPS2 PS1 PSO позиция IWCON.7 WCON.6 WCON.5 IWCON.3 WDTRST IWDTEN Регистр управления WCON имя и назначение 1Эти три бита устанавливают время пересброса контроллеоа сигналом от WDT. Соотношение между значениями битов и временем пересброса: ips2 ГуУСОЫ.4 WCON.2 WCON. Г IWCON.O IPSI Не используется Время пересброса, мс: 1024 12048 Не используется Й'зат^л?0РтТпяГ =° ° - указатель DPTR, расположенный в адресах 082Н, 083Н. Установка ьита 1 делает активным дополнительный указатель DPTR1 (084Н, Бит сброса содержимого счетчика сторожевого таймера Его- установка в 1 программой пользователя сбрасывает счетчик vcrHnlTJ \° ески в следующем цикле после установки его в 1. Бит только для записи ьбит включения/выключения сторожевого таймера (о - выключен) Примечание. Значение регистра при сбросе - 00000010В 170 g WDTRST. Отметим, что приведенные в табл. 12 расчетные периоды пересброса могут отличаться от реальных на 25...30 % как в ту, так и Б другую стороны. ПРОГРАММИРОВАНИЕ AT89S53 Микроконтроллеры AT89S53 допускают программирование как с использованием 12-вольтового интерфейса, так и 5-вольтового. Однако если у АТ89С51/52/55 для достижения подобной гибкости пришлось изготавливать различные версии изделий, допускаюгцих работу только с одним из интерфейсов, то каждый из AT89S53 содержит в себе обе эти возможности. Режим параллельного программирования идентичен тому, который предусмотрен для АТ89С51/52/55, использует 12-вольтовый сигнал Vpp. Пятивольтовая загрузка, делающая возможным перепрограммирование микроконтроллера в аппаратуре пользователя, использует для этого интерфейс SPI. В табл. 13 описаны сигналы программирования и верификации параллельного режима программирования AT89S53. Режим последовательного программирования реализуется следующим образом. На вход сброса подается сигнал высокого уровня. После этого по каналу SPI должна быть передана команда разрешения программирования (см. табл. 14). Отметим, что в этом режиме действует автоматическое предварительное стирание информации. Перед программированием какого-либо байта не надо стирать все содержимое ПЗУ - программируемый байт очищается сам перед записью. Напомним, что на параллельное программирование это, увы, не распространяется. Режим стирания очищает все содержимое ПЗУ, когда в него нужно занести новую программу, а не просто модифицировать отдельные коды. Частота SCK при программировании не должна превышать 1/40 частоты кварцевого резонатора. Перед выдачей команды разрешения программирования необходима задержка не менее 10 мс. Алгоритм программирования и верификации в рассматриваемом случае должен выглядеть так: 1. Подать напряжение питания. Установить вывод RST в 1. Если тактирование осуществляется внешним источником, подать тактовый сигнал (4...24 МГц) на XTAL1 и выдержать паузу 10 мс. 2. Разрешить последовательное программирование посылкой команда разрешения программирования. Частота тактирования на SCK должна быть в 40 и более раз ниже тактовой частоты на XTAL1. 3. Программирование внутренней памяти программ осуществляется побайтно.

I И s S S rt a. t О a с О о a. с га § ra a. s к s & 3 о 6 о X m ii  Для этого вначале в контроллер передается байт, в старших битах которого находятся биты старшего байта адреса, затем младший байт, после чего - байт данных. Информация о том, что должна произойти запись, содержится в двух младших битах первого переданного байта. Модифицируемый байт перед программированием автоматически стирается. 4. Верификация любого байта осуществляется командой чтения, содержащей адрес считываемой ячейки. Контроллер передает верифицируемый байт через свой выход MISO (PI.6). 5. После окончания программирования RST установить в 0. 6. Выключить питание. Схемы включения микроконтроллеров AT89S53 при программировании приведены на рис. L5 и 16, временные характеристики сигналов параллельного режима программирования - в табл. 16. AT89S8252/AT89LS8252 Эти микроконтроллеры почти повторяют AT89S53. Отличие состоит в объеме размещенной на кристалле памяти программ 8 кбайт и в присутствии в нем внешней 2-килобайтной Flash-памяти данных, доступной по командам MOVX. Количество циклов программирования первой составляет, как и у остальных контроллеров Atmel, - 1000. Ресурс второй увеличен на два порядка (100000 циклов стирания/записи), поскольку данные обновляются А0...А7 . (ООООН-27FFH) А8...А13 В соответствии с табл. 13 3...12 МГц т С2ф п А0...А7 (0000H-27FFH) L> А8...А13 В соответствии J с табл.13 J. С1: 3...12МГЦ X С2:

-о+5 в PGM DATA -PROG Upp UlH P2.0-P2.5 P2.6 P2.7 P3.6 P3.7 XTAL2 -O+S В Верифицируемые данные (выводы шины соединить с Ucc через резисторы сопротивлением ЮкОм) -UH Upp XTALl RSTL-UH GND PSEN Рис. 15. Программирование и верификация AT89S53 в режиме параллельного программирования AT89S53 Вход команд. Выход данных. Тактовые. импульсы BQICI 3...12 МГц т 02: P1.5/M0SI P1.6/MIS0 P1.7/SCK XTAL2 XTAL1 GND -0+2,7...6В UiH Рис. 16. Программирование и верификация AT89S53 в режиме последовательного программирования Временные характеристики циклов программирования и верификации

гораздо чаще самой программы. Энергонезависимая внешняя память данных, размещенная на кристалле, позволяет хранить константы, таблицы и другие данные, которые должны допускать возможность оперативного изменения в процессе работы без потери их при выключении питания. Параметры AT89S8252/AT89LS8252 приведены в табл. 17, цоколевка аналогична АТ89С51. Нагрузочная способность выводов аналогична АТ89С51/ AT89LV51. Напряжения на входах относительно общего провода должны лежать в диапазоне от -1 до +7 В; максимальное рабочее напряжение - 6,6 В. В режиме Power Down допустимо его снижение до 2 В. Потребление AT89S8252 на частоте 16 МГц при напряжении питания 6 В не превышает 25 мА, в режиме Idle - 6,5 мА, в режиме Power Down - 100 МК А при напряжении 6 В и 40 мкА при 3 В. Зависимость потребляемого тока от напряжения питания и частоты для AT89LS8252 аналогична приведеной на рис. 2. В микроконтроллерах AT89S8252 и AT89LS8252 сигнал ALE, как и в АТ89С51, можно программно запретить, установив в 1 бит О SFR-регистра, находящегося по адресу 8Е. Выводы порта РЗ выполняют те же альтернативные функции, что и у AT89S53. AT89S8252 и AT89LS8252 также снабжены SPI-интерфейсом, выполняющим все описанные выше функции. Они имеют аппаратный сторожевой таймер, работающий идентично таймеру AT89S53. a о и > ra I о о ra ra Q- I S if a: о ra ra с ffl Q- ra С Ш ц га 3-Ь о J3 га О ю 3 CD ю ю О- О- 0- о

00 СО Е - CD ю ю гм гм р о. 0-S m I I I s (0 a: S CD ч: о Ч о 3 о cl о о о m m со 03 Е , - О. 3 3 О О Регистровое пространство AT89S8252 и AT89LS8252 также, как у AT89S53 расширено в сравнении с предшественниками. В нем есть регистры, обслуживаюш,ие SPI и сторожевой таймер - SPCR (0D5H), SPSR (OAАН), SPDR (086Н) и WMCON (096Н). Добавлен еще один указатель DPTR (DP1L и DP1H, находящиеся по адресам 084Н и085Н соответственно). Переключение с основной регистровой пары на дополнительную и обратно осуществляется битом DPS в регистре WMCON. Поскольку в этом регистре находятся также биты управления Flash-памятью данных, его название несколько изменено в сравнении с AT89S53 - WMCON вместо WCON. Регистр управления сторожевым таймером и Flash-памятью данных описан в табл. 18. Таблица 18 Регистр управления WMCON

Примечание. Значение регистра при сбросе - 00000010В Для обращения к Flash-памяти данных необходимо установить в 1 бит EEMEN в регистре WMCON. В адресном пространстве внешней памяти Flash-памятью данных занимает область от ООООН до 07FFH. При обращении к ней и установленном бите EEMEN производится запись или считывание из Flash-памяти. Для обращении к обычной внешней памяти данных, расположенной в этих же адресах (если таковая имеется) необходимо предварительно запулить EEMEN. Перед записью байта во Flash-память данных необходимо установить в 1 бит EEMWE регистра WMCON. Если после какого-либо мо- мента ваша программа не должна больше записывать данные во Flash-память, рекомендуется сбросить этот бит, а не держать его постоянно во взведенном состоянии. Запись байта занимает примерно 2,5 мс. Пока запись не закончена, флаг RDY/ BSY в регистре WMCON сброшен. Его установка, т. е. единичное значение бита RDY/ BS Y свидетельствует о завершении текущего цикла записи и готовности к следующему. Кроме того, если запись во Flash-память данных не завершена, попытка считать байт по записываемому адресу дает значение, комплементарное записываемому. Как только запись окончена, считывание дает правильное значение. ОСОБЕННОСТИ ПРОГРАММИРОВАНИЯ AT89S8252 И AT89LS8252 Подобно AT89S53, AT89S8252 и AT89LS8252 допускают как параллельное (12-вольтовое) программирование, так и последовательное (5-вольтовое), ориентирование на перепрограммирование ПЗУ в аппаратуре пользователя. Но есть и отличие. Последние имеют два массива Flash-памяти - внутренняя память программ и внешняя с точки зрения системы команд, но находящаяся внутри кристалла, память данных. Оба режима программирования допускают занесение информации как в тот, так и в другой массив. Но если при последовательном программировании эти массивы находятся в разных адресных пространствах и для каждого из них предусмотрен свой набор команд чтения/записи (см. табл. 20), то при параллельном программировании их адресное пространство едино. При этом память команд занимает адреса с ООООН по 1FFFH, а Flash-память данных - с 2000Н по 27FFH. Таким образом, в последнем режиме пользователь как-бы имеет контроллер с 10-килобайтной внутренней памятью, подлежащей программированию, при этом первые 8 кбайт содержат коды программ и таблицы констант, а последние 2 кбайта - оперативные данные, которые могут изменяться самим контроллером в процессе его работы. Соответственно, если необходимо предварительное занесение информации во Flash-память данных (вместе с программированием ПЗУ контроллера), эти данные должны быть внесены в загружаемый в программатор файл в соответствующие адреса, и диапазон программируемых адресов устанавливается от ООООН до 27FFH (10 кбайт). Возможно отдельное программирование Flash-памяти данных в программаторе - загружаемый в него файл должен содержать только байты памяти данных, а диапазон устанавливаемых адресов - лежать от 2000Н до 27FFH. Напомним, что при последовательном программировании нет необходимости стирать перед записью предварительно заносившуюся в контроллер информацию, в то время как при параллельном необходима предварительная очистка содержимого Flash-памяти. В табл. 19 описаны сигналы программирования и верификации параллельного режима программирования AT89S53. Режим последовательного программирования реализуется как и для AT89S53. На вход сброса подается сигнал высокого уровня. После этого по каналу SPI должна быть передана команда разрешения программирования (см. табл. 20). Напомним, что в этом режиме перед программированием какого-либо байта не надо стирать все содержимое ПЗУ - программируемый байт очищается перед записью сам. ОЧЕРЕДНЫЕ ДОСТИЖЕНИЯ ФИРМЫ ATMEL В ОБЛАСТИ МИКРОКОНТРОЛЛЕРОВ СЕМЕЙСТВА Х51 Микроконтроллеры фирмы Atmel [1, 2] семейства х51 являются в настоящее время, пожалуй, наиболее популярными микроконтроллерами среди отечественных разработчиков. Еще до появления первых микроконтроллеров семейства х51 фирмы Atmel, это семейство уже занимало лидирующие позиции на отечественном и зарубежном рьшке. Это обусловлено целым рядом причин. Во-первых, семейство х51 de facto является всемирным промышленным стандартом и широко распространено во всем мире. Во-вторых, к тому времени было опубликовано достаточно много разнообразной научно-технической литературы (статей, рекомендаций по применению, книг) по аппаратной реализации этих микроконтроллеров, их программированию и применению, как зарубежных, так и отечественных авторов. В третьих, за время существования этого семейства для него бьшо разработано очень большое количество качественного и доступного программного обеспечения: компиляторов (ASM51, С-Н-, PL/M51, Fort51 и т. п.), дизассемблеров, программных отладчиков, эмуляторов и т. п. В четвертых, у большинства разработчиков, занимающихся микроконтроллерной техникой, уже имелся достаточно большой опыт общения с этим семейством микроконтроллеров, изучены многие особенности  о я ш о о. (О а о а. с О i; н с; и о с

2 Ф Ф О сл с < о ф CL Л § га t->s я ю <£ i о 1 11 Ci Ф I § 5ю ? 1 Ф го 1 2- их поведения, выработаны приемы и способы отладки, накоплен опыт программирования, у многих из них уже существовали большие оригинальные библиотеки программ для различных научно-технических задач. Появление АТ89 микроконтроллеров фирмы Atmel, изготовленных по КМОП (CMOS) технологии, имеющих полностью статическую структуру и оснащенных встроенной Flash-памятью программ еще более усилило позиции х51совместимых микроконтроллеров. Первое поколение семейства АТ89 насчитывало 15 типов микроконтроллеров (намай 1998 г.). Оно включало в себя три группы микроконтроллеров: группу перепрограммируемых микроконтроллеров (Reprogrammable Flash) AT89C(LV)51/52/55; группу перепрограммируемых микроконтроллеров в малом корпусе с сокращенным количеством выводов (Small Footprint, Reprogrammable Flash) AT89C1051/1051U/ 2051/4051; a также группу микроконтроллеров с внутрисистемным программированием (1п-System Programmable (ISP) Flash) AT89S(LS)53/8252 и AT89S4D12. Появление этого поколения микроконтроллеров значительно облегчило жизнь разработчиков на этапе написания и отладки программного обеспечения за счет наличия встроенной Flash памяти программ с достаточно простой процедурой программирования. Кроме того, использование микроконтроллеров АТ89 позволило получить более высокие результаты при создании микро-контроллерньгх систем в плане снижения энергопотребления (за счет полностью статической структуры микроконтроллеров) и сокрапдения аппаратных затрат (за счет наличия встроенной Flash памяти различного объема и отсутствия необходимости в дополнительных логических элементах для организации внешней подсистемы памяти программ). Вышеперечисленные преимущества сделали первое поколение семейства АТ89 неимоверно популярным (особенно первые две группы). За последние несколько лет фирма Atmel создала достаточно много новых интересных микроконтроллеров семейства х51 - так называемое второе поколение. На сегодняшний день семейство представлено двеннадцатью группами, включающими около 70 микроконтроллеров! Прежде чем ознакомиться с каждой из групп, необходимо ознакомиться с принятой терминологией, основными сокращениями и понятиями. Многие из микроконтроллеров фирмы Atmel оснащены встроенной Flash памятью программ - IROM (Internal ROM) и встроенной основной оперативной памятью - IRAM (Internal RAM). Некоторые современные микроконтроллеры второго поколения имеют кроме IRAM еще и встроенную дополнительную оперативную память - XRAM (Extended RAM), что безусловно делает эти микросхемы еще более мощными и привлекательными. Кроме того, некоторые микроконтроллеры имеют встроенную Flash память данных - IDROM (Internal Data ROM), которая может использоваться для хранения настраиваемых параметров, сетевых адресов и другой информации. Практически все микроконтроллеры со стандартным или расширенным набором линий ввода/вывода (или портов) обладают возможностью работы с внешней памятью программ или данных. В приведенных ниже таблицах в графе ЕМ (External Memory) плюсом отмечена такая возможность. Если в этой колонке проставлен минус - микроконтроллер не может работать с внешней памятью. Как правило, это связано с уменьшенным (ограниченным) количеством линий ввода/вывода вследствие исполнения микросхем в маловыводном корпусе. Микроконтроллеры семейства х51 в стандартной конфигурации (в стандартных корпусах) обеспечивают работу с внешней памятью объемом до 64К. Микроконтроллеры, у которых в соответствующей колонке проставлен другой меньший объем памя- хи имеют уменьшенное количество линий ввода/вывода. Если объем адресуемой памяти больше 64К, микроконтроллеры имеют расширенную шину адреса или аппаратный диспетчер памяти. Различные микроконтроллеры имеют различное количество портов ввода/вывода, и соответственно, различное количество линий ввода/вывода-I/O (Input/Output Lines). Микроконтроллеры семейства х51 в стандартной конфигурации имеют 4 порта или 32 линии ввода/вывода. У других микроконтроллеров количество линий может отличаться в большую или меньшую сторону. Все микроконтроллеры семейства х51 имеют встроенных последовательный порт - SP (Serial Port). Наличие плюса в одноименной колонке означает наличие стандартного последовательного порта. Некоторые микроконтроллеры в соответствующей колонке имеют вместо плюса букву Е (Enhanced) - с расширенными возможностями, например, с автоматическим обнаружением ошибки фрейма, автоматическим определением адреса, с специализированным генератором скорости передачи и т.д. Все микроконтроллеры семейства х51 имеют несколько таймеров/ счетчиков общего назначения Т/С (Timer / Counter) и источников прерывания IS (Interrupt Source). Количество этих периферийных устройств указано в соответствующих колонках. В некоторых микроконтроллерах имеется также встроенный аппаратно реализованный последовательный периферийный интерфейс - SPI (Serial Peripheral Interface). Для выхода из возможных состояний зависания микроконтроллера служит аппаратно реализованный сторожевой таймер WDT (Watchdog Timer), включаемый в состав периферийных узлов многих микроконтроллеров второго поколения. В некоторых микроконтроллерах, выпускаемых в малых корпусах с сокращенным набором линий ввода/вывода (Small Footprint), имеется встроенный аналоговый компаратор - АС (Analog Comparator). Некоторые современные микроконтроллеры оснащаются двумя регистрами-указателями данных DPTR (Data Pointer Register), что позволяет создавать для них более эффективное программное обеспечение. Большинство микроконтроллеров первого поколения программировались на специальных параллельных программаторах. Многие микроконтроллеры второго поколения позволяют производить программирование непосредственно в изделии через специальный узел - ISP (In-System Programmable Flash). При этом процедура программирования предполагает подачу на микроконтроллер некоторых управляющих сигналов. Некоторые последние версии микроконтроллеров имеют так называемую загрузочную программу (Boot), упрощающую режим программирования. в последнее время, наряду с перепрограммируемыми Flash-микропроцессорами, фирма Atmel выпускает также так называемые однократно программируемые Flash-микропроцессоры (без возможности стирания Flash памяти) - OTP (One-Time Programmable), микроконтроллеры с масочным ПЗУ (ROM), запрограммированным на этапе производства и микроконтроллеры без встроенной памяти программ (ROMless), обеспечивая тем самым все потребности рынка. Рассмотрим современное состояние семейства х51 микроконтроллеров. Первая группа микроконтроллеров - перепрограммируемые микроконтроллеры с Flash-памятью программ в стандартном корпусе (см. табл. 21) практически не изменилась, за исключением того, что в нее включены микроконтроллеры AT89C55WD AT89C51RC, со-держагцие 20К и 32К Flash-памяти программ, аппаратно реализованный WDT, оснагценные два DPTR и работаюгцие на частотах до 33 МГц. По оценкам экспертов, наибольшей популярностью в этой группе пользуется стандартный АТ89С52 микроконтроллер. Таблица 21 Перепрограммируемые Flash микроконтроллеры в стандартном корпусе

Вторая группа микроконтроллеров в малогабаритном корпусе с усеченным набором портов приведена в табл. 22. Наиболее популярен в этой группе микроконтроллер АТ89С2051, обеспечиваюгций наилучшее соотношение цена/качество. Третья группа микроконтроллеров с внутрисистемным программированием ( табл. 23), пожалуй, является наиболее интересной для широкого круга разработчиков. В эту группу входят и известные читателю микроконтроллеры первого поколения AT89S53 и AT89S8252 (и их аналоги с пониженным напряжением питания AT89LS53 и AT89LS8252), и аналоги микроконтроллеров первой группы АТ89С51/52 с добавленной возможностью внутрисистемного программирования - AT89(L)S51/ 52, и ряд новых малоизвестных микроконтроллеров T89C51RB2/RC2/ RD2/IC2/AC2. Главными отличиями этих новых микроконтроллеров (Т89С51ххх) являются два DPTR, встроенный аппаратный WDT, встроенный режим ISP, большой объем Flash памяти программ, наличие у части из них дополнительной оперативной памяти данных XRAM (-1-1 кбайт), встроенного последовательного порта с дополнительными возможностями. Кроме того, все они оснагцены так называемым Х2 режимом ускорения (машинный цикл содержит 6 тактов, а не 12, Таблица 22 Перепрограммируемые Flash микроконтроллеры в малогабаритном корпусе

как у стандартного семейства х51). Это позволяет им на тактовой частоте 20 МГц работать также быстро, как стандартные микроконтроллеры работали бы на частоте 40 МГц. В то же время, они могут работать и в стандартном режиме (12 тактов/цикл) на частотах до 40 Мгц. Микроконтроллеры RC2 и RD2 имеют дополнительную загрузочную память с программой загрузки Boot, что значительно упрогцает программирование. Микроконтроллер RD2 в увеличенном корпусе имеет 1 ... 6 7 8 9 10 11 12 ... 20 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2024 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |