|

|

|

Разделы

Публикации

Популярные

Новые

|

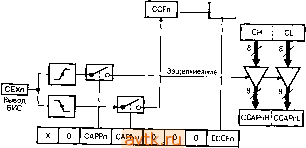

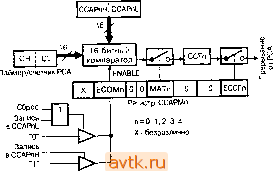

Главная » Классические однокристальные микроконтроллеры 1 ... 3 4 5 6 7 8 9 ... 20 Каждый модуль имеет, кроме того, пару собственных 8-битных регистров сравнения-защелки (ССАРпН и CCAPnL). В этих регистр pax запоминаются показания таймера РСА в момент прихода сигнала на защелкивание информации или содержатся данные для сравнения с показаниями таймера-счетчика. В ШИМ-режиме старший байт ССАРпН управляет скважностью импульсов. Режим защелки РСА Осуществлять защелкивание информации можно как положительным, так и отрицательным перепадом импульса, что делает РСА весьма гибким инструментом для измерения периода следования сигналов, ширины импульса, скважности и фазовых задержек между импульсами, приходящими по пяти входным цепям. Установка битов САРРп и/или CAPNn в регистре ССАРМп выбирает, каким перепадом будет осуществляться защелкивание информации - фронтом и/или спадом импульса в модуле п. л-Г1 Прерывание  Регистр ССАРМп п = 0,1,2,3,4 X - безразлично Рис. 3 Управление защелкиванием информации осуществляется импульсами на внешних выводах СЕХ0-СЕХ4. Когда надежно выделен перепад сигнала (фронт или спад), происходит аппаратная загрузка 16-битного значения счетчика РСА (CH,CL) в регистры ССАРпН, CCAPnL соответствующего модуля сравнения-защелки. Результирующее значение этих регистров отражает значение счетчика РСА в момент выделения перепада сигнала на внешнем выводе СЕХп. При защелкивании устанавливается в один связанный с соответствующим модулем флаг CCFn в регистре CCON. Если при этом установлен флаг ECCFn в регистре ССАРМп, то формируется вызов прерывания от РСА (естественно, если оно не замаскировано). Так 106 как аппаратно этот флаг не сбрасывается после того, как подпрограмма обработки прерывания вызвана, его нужно сбросить программным путем в ходе выполнения этой подпрограммы. В ходе этой подпрограммы 16-битовое значение, записанное в ССАРпН, CCAPnL должно быть переписано в ОЗУ микроконтроллера до того, как придет новый фронт или спад, вызывающий следующее защелкивание информации в упомянутых регистрах. Если этого не сделать, новая информация записывается поверх имеющейся, и последняя теряется. . Время, необходимое для вышеупомянутых действий, ограничено тактовой частотой микроконтроллера. Запоминание двух 8-битовых регистров и сброс флага требует 9 машинных циклов (сюда входит и вызов прерывающей программы). Таким образом, для тактовой частоты 12 МГц защелкивание не может быть чаще, чем один раз в 10 мкс. Режим программируемого таймера В большинстве применений программируемый таймер используется для вызова прерывающей программы, которая должна выполняться с постоянным заданным интервалом. Пользователь осуществляет предварительную загрузку 16-битового значения в  Рис. 4 ССАРпН, CCAPnL. В режиме, когда на вход модуля подан сигнал с частотой, равной частоте задающего генератора, деленной на 4, сравнение производится трижды в течение каждого машинного цикла. Для разрешения сравнения необходимо установить в 1 бит ЕСОМп 8 регистре ССАРМп. Для функционирования модуля в упомянутом режиме также необходимо установить в 1 бит МАТп в ССАРМп. Когда наступает со- впадение информации в ССАРпН, CCAPnL с содержимым СН, CL, вырабатывается сигнал совпадения и устанавливается флаг CCFn. Если при этом установлен бит ECCFn, то будет вызвана прерывающая программа (естественно, если прерывание от РСА не запрещено). Флаг CCFn должен быть сброшен программно до того, как произойдет новое совпадение информации в таймере и регистрах модуля сравне-ния-загцелки. Если подпрограмма прерывания заносит новое значение в ССАРпН, CCAPnL, флаг ЕСОМп автоматически сбрасывается, как только информация заносится в CCAPnL. Запись в ССАРпН снова устанавливает этот бит в 1, разрешая, таким образом, работу компаратора. По этой причине пользовательская программа должна вначале заносить информацию в CCAPnL, а затем в ССАРпН, а не наоборот, чтобы исключить вызов прерывания в тот момент, когда новое значение информации окончательно не занесено в CCAPnL, ССАРпН. Режим высокоскоростного выхода В режиме высокоскоростного выхода происходит переключение вывода СЕХп с 1 в О и наоборот в момент совпадения информации в регистрах таймера РСА СН и CL и в регистрах модуля сравнения-защелки ССАРпН, CCAPnL. Для реализации этого рекима необходимо установить в 1 биты ЕСОМп, МАТп и TOGn в регистре ССАРМп. Предварительно установив вывод СЕХп в О или в I, пользователь выбирает, каким перепадом на нем будет сопровождаться равенство информации в СН, CL и ССАРпН, CCAPnL. Помимо перепада на выводе СЕХп, пользователь может также вызвать подпрограмму прерывания для выполнения определенных функций микроконтроллером при вышеупомянутом совпадении значений в регистрах. С этой целью должен быть установлен флаг ECCFn и разрешено прерывание от РСА. В этом режиме возможно более точное фиксирование равенства информации в таймере РСА и в модуле сравнения-защелки, чем при программной установке внешнего вывода в ходе выполнения подпрограммы прерывания, определившей факт совпадения информации. Иными словами, в этом режиме не сказывается скорость отработки программы прерывания. Эта подпрограмма нужна в том случае, когда пользователь хочет изменить информацию в СС;АРпН, CCAPnL. Еаш эту информацию не менять, то следую-;ц!1Й сигнал появится только тогда, когда таймер РСА досчитает до своего максимума и начнет счет сначала. При частоте сигнала 16 МГц частота повторения сигналов в режиме быстрого отклика равна 30,5 Гц. Режим сторожевого таймера Функцию сторожевого таймера может выполнять только модуль 4 сравнения-защелки. Если в сторожевом таймере нет необходимости, модуль можно использовать аналогично остальным модулям. Сторожевой таймер представляет из себя цепь, которая вызывает автоматический сброс, если система не пришлет таймеру регулярный сигнал, подтверждающий нормальное функционирование. Эту цепь используют устройства, которые работают с электрическими шумами, бросками питающего напряжения, электростатическим разрядом и т. д. или требующие повышенной способности к самовосстановлению системы. В этом режиме в тот момент, когда содержимое таймера РСА равно значению в ССАР4Н, CCAP4L, генерируется внутренний сигнал сброса. Для задания этого режима нужно установить в 1 бит WDTE в регистре CMOD. При этом модуль 4 сравнения-защелки должен быть сконфигурирован либо на функционирование в режиме программируемого таймера, либо в режиме высокоскоростного выхода. ССАРпН 1 CCAPnL Таймер/счетчик РСА СН ; CL 16 - битный компаратор

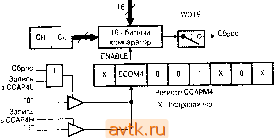

Запись I в CCAPnL О-. Запись в ССАРпН- 1 . Вывсд БИС -{clxiri Таймер/счетчик РСА

Регистр ССАРМп п-0,1,2,3,4 X - безразлично  Рис. 5 Рис. 6 Сброс при работающем сторожевом таймере не произойдет в следующих трех случаях: >. при периодическом изменении значения в ССАР4Н, CCAP4L таким образом, чтобы вновь записанное значение до новой записи не могло совпасть с СН, CL; при периодическом изменении СН, CL с тем же результатом; при установке в О бита WDTE перед сбросом и повторной установка его в 1 после того, как значения СН, CL сравнялись с ССАР4Н, CCAP4L. Первые два случая - более подходящие для таких систем, которые критичны к зависанию, т. к. в этих случаях сторожевой таймер не отключается. При этом второй вариант не рекомендуется, если таймер РСА используется еще каким-либо модулем сравнения-защелки. Таким образом, первый случай наиболее применим для практической реализации. Режим широтно-импульсного модулятора Любой из пяти модулей РСА может быть запрограммирован в режим ШИМ. Выход ШИМ может быть использован для преобразования цифровых данных в аналоговый сигнал с минимальными дополнительными аппаратными затратами. Частота модуляции зависит от скорости счета таймера РСА. С 16 МГц кварцевым резонатором максимальная частота сигнала ШИМ не превышает 15,6 кГц. Для работы в режиме ШИМ биты ЕСОМп и PWMn в регистре ССАРМп должны быть установлены. РСА вырабатывает 8-битный ШИМ-сигнал путем сравнения содержимого CCAPnL и CL. Если CL<CCAPnL, то на внешнем выводе соответствующего модуля сравнения-защелки будет сигнал с нулевым уровнем, если CL>CCAPnL, то с единичным. Значение, записанное в CCAPnL задает скважность формируемого сигнала. Для изменения значения CCAPnL без сбоев пользователь должен занести требуемое значение в ССАРпН. Это значение аппаратно заносится в CCAPnL в момент, когда CL меняет свое значение с FFH на О, что соответствует началу нового выходного цикла. В ССАРпН можно занести любое целое число от О до 255, при этом скважность меняется от 100 до 0,4 %. Нулевая скважность обеспечивается путем прямой записи информации в SFR соответствующего порта. Значение ССАРпН, при котором достигается требуемая скважность, определяется соотношением ССАРпН= 256(1 - скважность). Запись JL перепадом -\ / изРРвОО y CCAPnL И Восьмибитный компаратор CL< CCAPnL Вывод БИС СЕХг> ENABLE Р п-0,1,2,3,4 X - безразлично CL> CCAPnL

Регистр ССАРМп Рис. 7 где ССАРпН - ближайшее целое число к значению в правой части выражения (*), скважность представляет собой величину в диапазоне от О до 1. На рис. 8 приведены зависимости сигналов на выходе микроконтроллера при работе РСА в режиме ШИМ и при различных значениях информации в ССАРпН. Скважинность ССАРПН Выходной сигнал микроконтроллера 100% 00 90% 50% 10% 0,4% 25 128 230 255 Л П-TL Рис. 8 МИКРОКОНТРОЛЛЕРЫ ГРУППЫ 8XC51GB ФИРМЫ INTEL Выше мы познакомили читателей с микроконтроллерами групп 8xC51Fx, 8xL5lFx фирмы Intel, являющимися одними из самых совершенных изделий в семействе MCS-51. Теперь речь пойдет о последней ее группе контроллеров этого семейства - 8xC51GB. Пожалуй, именно при создании этих контроллеров разработчики Intel пришли к выводу, что простое наращивание аппаратных ресурсов у вновь разрабатываемых изделий без существенной доработки архитектуры семейства не приносит пользователям ощутимого вьшгры- ша, особенно в вопросах повышения производительности и расширения возможностей. В связи с этим и появились микроконтроллеры семейства MCS-2 51. Многие пользователи с эн тузиазмом восприняли его появление. Но, по мнению автора, и 8xC51GB - наиболее необычный член семейства MCS-51 - все же интересен в силу чрезвычайно широких по меркам микроконтроллеров аппаратных возможностей, о которых будет рассказано ниже. В состав группы входят следующие изделия: 80C51GB, 83C51GB, 87C51GB, 80C51GB-1, 83C51GB-1, 87C51GB-1. На момент подготовки материала все эти изделия выпускались в 68-выводном корпусе PLCC и маркировались с префиксом N (N80C51GB). Кристаллы выполнены по CHMOS Ш-Е технологии фирмы Intel. Версии с программируемым внутренним ПЗУ не имеют прозрачного окна в корпусе, т. е. относятся к разряду однократно программируемых. Это несколько ограничивает круг их потребителей в силу того, что при отладке не удается работать методом проб и ошибок с многократным перепрограммированием кристалла, а обязательно приходится использовать соответствующий эмулятор. Первые три из перечисленных выше контроллеров работают при частоте тактового сигнала в диапазоне от 3,5 до 12 МГц. Вторые три контроллера, имеющие единичку в конце маркировки, работоспособны при частоте от 3,5 до 16 МГц. Все упомянутые контроллеры - 5-вольтовые, низковольтных версий выпущено не было. Характерные отличительные особенности группы 8xC5lGB следующие: объем резидентной программной памяти - 8,16 или 32 кбайта; объем резидентной памяти данных - 256 Байт; 48 линий ввода/вывода (6 8-битных портов), из которых 40 снабжены триггерами Шмитта во входной цепи; три 16-битных таймера-счетчика, при этом третий может дополнительно работать в следующих режимах: программируемого частотного выхода; таймера-счетчика с возможностью прямого и обратного счета; два массива программируемых счетчиков (РСА и РСА 1), работающих в следующих режимах: сравнения/защелкивания; программируемого таймера; высокоскоростного выхода; широтно-импульсного модулятора; 15 векторов прерываний; 4-уровневая структура прерываний; дуплексный программируемый последовательный порт, поддерживающий: . автоматическое распознавание адреса; . детектирование ошибок формата ( потерю стоп-бита); 8-битный 8-канальный АЦП; два режима уменьшенного энергопотребления; тестовый режим эмуляции ONCE ; программирование по улучшенному алгоритму быстрых пульсаций ; 3-уровневая система защиты памяти программ; расширенный последовательный порт; специализированный аппаратный сторожевой таймер; система распознавания сбоя тактового генератора. Большинство из перечисленных особенностей относится ко всему семейству MCS-51, в связи с чем мы не будем подробно на них останавливаться. Кроме того, выше, при анализе микроконтроллеров семейства 8хС51Ех, 8xL5lFx, нами был подробно описан массив программируемых счетчиков, в связи с чем он также будет рассмотрен нами только с точки зрения его отличий от имеющегося в 8хХ51Ех. Предметом нашего знакомства будут те из особенностей 8xC51GB, которых нет больше ни у одной из групп MCS-51. Отметим, что 80C51GB и 80C51GB-1 не имеют внутренней памяти программ. 83C51GB и 87C51GB имеют по 8 кбайт масочно программируемого и перепрограммируемого ПЗУ соответственно. У 83C51GB-1 и 87C51GB-1 объем (опять-таки соответственно) масочного и перепрограммируемого ПЗУ составляет 16 и 32 кбайта. РАСПОЛОЖЕНИЕ И НАЗНАЧЕНИЕ ВЫВОДОВ Расположение и назначение выводов приведены в табл. 6. Большинство из упомянутых выводов знакомы тем, кто уже имел дело с микроконтроллерами MCS-51. Новыми являются выводы портов Р4, Р5 со своими альтернативными функциями (они приведены после слэша ) и сигналы, связанные с АЦП (Avref, Avss, COMPREF, АСН0...АСН7, TRIGIN). Эти сигналы будут рассмотрены ниже при описании соответствующих устройств. Порт РО аналогичен соответствующим портам более ранних микросхем и выполняет те же функции. У 8xC5lGB появились два новых порта - Р4 и Р5. Все порты Р1 -Р5 являются 8-битовыми квазидвунаправленными портами ввода/вывода, с мощным внутренним резистором, обеспечивающим быстрое установление на выходах уровня логической единицы при переключении. Резистор подключается к выходному каскаду на два периода тактового генератора для перевода вывода в ука- занное состояние, а затем отключается. Выводы портов Р1-Р5, находящиеся в состоянии логической единицы, имеют высокий потенциал за счет внутреннего резистора и могут использоваться в этом состоянии как входы. В отличие от порта РО, входные линии портов Р1 - Р5 снабжены входными триггерами Шмитта. Почти все выводы портов имеют альтернативное назначение (см. табл. 7). При сбросе выводы порта РЗ устанавливаются в состояние логической единицы, выводы остальных портов - в нулевое состояние. Вход RESET - сброс. Низкий уровень на данном входе в течение двух машинных циклов при работающем тактовом генераторе приводит к сбросу контроллера. Выводы портов будут приведены в исходное состояние в тот момент, когда напряжение на этом входе снизится до 0,3...0,4 В. Процедура сброса длится 5 машинных циклов (60 периодов тактового генератора). Необходимо обратить внимание на то, что полярность сигналов сброса для микроконтроллеров группы 8xC81GB обратная по отношению к другим членам семейства MCS-51. Причины этой инверсии автору неизвестны. Внутренний резистор соединяет этот вход с общим проводом. Внешний конденсатор RC-цепочки должен соединять вход RESET с Vss. Вход ALE/ PROG полностью аналогичен соответствующему входу других членов семейства MCS-5L Отметим, что в 8xC51GB пользователь имеет возможность запретить выдачу сигнала ALE путем установки в О младшего бита из регистра SFR, расположен-114

ного по адресу 8ЕН. При этом ALE выдается только в момент действия команд MOVC или MOVX, а в остальных случаях на этом выводе удерживается единичный уровень. Если вы работаете только с внутренней памятью программ и данных, на выходе ALE вообще не будет никаких сигналов. Вход EA/Vpp служит для разрешения выборки команд из внутренней памяти программ, если таковая имеется на кристалле, и вход соединен с общим проводом. При подаче на него единичного уровня вьшол- няется программа из внешней памяти программ. Однако последнее возможно только до того момента, пока не установлены биты защиты внутренней памяти программ, о чем будет сказано ниже. На этот вывод подается напряжение программирования Vpp= 12,75 В при программировании внутреннего ПЗУ микросхем 87C51GB, 87C51GB-1. ОТЛИЧИЯ КРИСТАЛЛОВ exCSIGB ОТ ОСТАЛЬНЫХ ЧЛЕНОВ СЕМЕЙСТВА MCS-51 Итак, перечислим наиболее существенные отличия 8хС5 ] GB. Это: запрет выдачи сигнала ALE по адресу 8ЕН; порт расширения последовательных каналов SEP; 8-канальный АЦП; два дополнительных 8-битных порта Р4 и Р5; пять дополнительных внешних прерываний JNT2... INT6; наличие 15 векторов прерываний; аппаратный сторожевой таймер; возможность определения сбоя тактового генератора; два массива программируемых счетчиков - РСА и РСА 1. 8xC51GB имеет режим холостого хода (XX) и пониженного энергопотребления (МП). В табл. 8 показано состояние выводов микроконтроллеров при переводе их в эти режимы. Таблица 8

УЗЕЛ АЦП АЦП мшсроконтролтера 8xC51GB имеет 8 аналоговых входов (выводы АСН0...АСН7), вход внешнего запуска TRIGIN, выводы питания и земли аналоговой части (AVref и AVss), развязанные гальванически с соответствующими выводами цифровой части, а также вывод опорного напряжения сравнения COMPREF. Внутренние цепи содержат 8-канальный мультиплексор, 256-элементную резистивную линейку, компаратор, устройство выборки/хранения, 8 регистров результата, регистр последовательного приближения, регистр результата сравнения. Функциональная схема АЦП приведена на рис. 9. Фактически в пространстве SFR имеется 10 дополнительных регистров. Регистры AD0...AD7 (84Н, 94Н, 0А4Н, 0В4Н, 0С4Н, 0D4H, 0Е4Н, 0F4H) содержат результаты преобразования по каждому из 8 каналов. Значение каждого регистра обновляется по завершению пре- образования в соответствующем канале, начиная с канала 0. Регистр результатов сравнения АСМР (0С7Н) содержит 8 флагов, отражающих результаты сравнения значения аналоговых входов АСН0-АСН7 со входом COMPREF (табл. 9). Соответствующий флаг устанавливается в 1 в том случае, если входное напряжение на этом аналоговом входе превышает COMPREF, в противном случае флаг сбрасывается. Регистр ACON (097Н) содержит флаг прерывания АЦП AIF, бит разрешения преобразования АСЕ, два бита выбора канала ACSO и ACS1, биты режима входа AIM и режима запуска ATM (табл. 10). TRIGIN - AFref -АСЕ- АСНО-АСН1 АСН2 АСНЗ АСН4 АСН5 АСН6 АСН7 Циклический П ! запуск АЦП COMPREF ACON 1 АСМР К AVss Рис. 9 Таблица 9

Таблица 10 Бит АСЕ Позиция AC0N.7 AC0N.6 AC0N.5 AC0N.4 ACS1 ACSO AC0N.3 AC0N.2 AC0N.1 Функция Зарезервирован Зарезервировен Флаг прерывания. Устанавливается в 1 по окончании преобразования в 7 канале. Будет вызывать прерывание в случае разрешения прерывания от АЦП Бит разрешения преобразования. При сбросе в О преобразование прекращается АС81=0, ACSO=0 - канал АСНО; АС81=0, АС80=1 - канал АСН1 ACS1=1, ACSO=0 -канал АСН2; ACS 1=1, ACS0=1 -канал АСНЗ ACON.0 Бит режима входа АЦП: О - режим сканирования, 1 - режим выбора канала pawjwa t\anaj ц -- . Бит режима запуска АЦП: О - режим внутреннего запуска, 1 - режим внешнего запуска -- Режим сравнения АЦП Этот режим всегда активен и используется для сравнения напряжений на входах АСН0-АСН7 с опорным напряжением, подаваемым на вход COMPREF контроллера. При всяком запуске аналого-цифрового преобразователя состояние каждого бита регистра АСМР устанавливается в новое состояние, начиная с канала О, независимо от типа установленного режима опроса каналов. Режим позволяет быстро осуществить сравнение типа больше-меньше двух аналоговых сигналов аппаратным методом, что может существенно сократить и упростить выполняемую программу. При отсутствии необходимости использовать режим сравнения на вход COMPEER можно подать любое напряжение от Vcc до Vss. Режим запуска АЦП Запуск преобразователя возможен как от внутреннего, так и от внешнего источника. Для реализации внутреннего запуска бит ATM регистра ACON должен быть установлен в 1. В этом режиме в цикле, следующем за тем, в котором бит АСЕ был установлен в 1, начинается преобразование с канала 0. После завершения преобразования в седьмом канале устанавливается флаг прерывания AIF. Если прерывание от АЦП разрешено, установка флага в 1 вызывает прерывание по вектору АЦП. Новый цикл преобразования начинается после завершения предыдущего. Установка бита АСЕ в О завершает преобразование. В режиме внешнего запуска преобразование начинается при наличии нулевого уровня на входе TRIGIN. На этом входе нет схемы фиксации перепада, и его состояние определяется путем опроса в каждом машинном цикле. Другими словами, для запуска преобразования нулевой уровень на входе TRIGIN должен иметь длительность более одного машинного цикла. После запуска цикла преобразования до его завершения состояние входа TRIGIN игнорируется, и преобразование осуществляется также, как и в предыдущем случае, до завершения преобразования в седьмом канале. После завершения цикла преобразования АЦП переходит в состояние останова до нового импульса на входе TRIGIN или до внутреннего запуска битом АСЕ. Режим входа АЦП Установка бита AIM в О переводит АЦП в так называемый режим сканирования. При этом преобразование осуществляется в порядке АСНО, АСН1,АСН7. Результаты преобразования помещаются соответственно в регистры ADO, AD1,AD7. При установке бита AIM в 1 после старта АЦП производятся 4 последовательных преобразования сигнала в канале, номер которого определяется состоянием битов ACSO и ACS1 регистра ACON. Результаты этих 4-х измерений сигнала в выбранном канале записываются в регистры AD0-AD3. После этого АЦП производит опрос каналов АСН4-АСН7, как и в режиме сканирования, результаты преобразования заносятся в AD4-AD7. Использование АЦП с меньшим количеством каналов Имеется несколько вариантов использования АЦП с меньшим, чем исходные 8, числом каналов. Если время преобразования не критично, то можно просто дождаться прерывания после завершения преобразования в седьмом канале и считать результаты только из выбранных каналов. Если важно получить результат сразу после завершения преобразования в выбранном канале, то 1п|:е1 предлагает производить отсчет нужного временного интервала с использованием таймера и его прерываний. Еще один рекомендуемый способ - периодический опрос состояния соответствующего регистра результата. Его изменение дает информацию о том, что произошло новое преобразование (правда, этот способ годится только в том случае, если измеряемое напряжение непостоянно). Использование режима выбора канала не уменьшает время преобразования, а лишь увеличивает количество измерений в выбранном канале за один цикл. АЦП в режиме микропотребления В состав АЦП 8xC5lGB входит цепь, ограничивающая энергопотребление узла в режимах снижения потребления до значения тока утечки. Для нормального функционирования этой цепи на вывод AVref микроконтроллера нужно подать потенциал Vcc. В течение режима пониженного потребления в этом случае напряжение питания можно уменьшать до минимального значения. МАССИВЫ ПРОГРАММИРУЕМЫХ СЧЕТЧИКОВ В состав микроконтроллера BxCSlGB входит массив программируемых счетчиков (РСА), аналогичный тому, который рассматривался нами при знакомстве с микроконтроллерами 8хС51Ех. Однако у 8xC51GB есть еще и второй аналогичный массив программируемых счетчиков (РСА1), практически не отличающийся от первого. Отличия РСА1 от РСА заключаются в следующем: модуль 4 РСА1 не поддерживает режим сторожевого таймера; внешними выводами РСА1 являются выводы Р4.2-Р4.7 (табл. 7); Таблица 11 названия всех регистров РСА1 и их битов содержат в имени единицу (табл. 11); в регистре управления РСА1 С ICON в пятой позиции имеется дополнительный бит CRE (битовый адрес OEDH). При установке его в единицу разрешение работы РСА1 происходит при совместной установке битов CR и CR1. СИСТЕМА ПРЕРЫВАНИЙ 8XC51GB Микроконтроллеры 8XC51GB поддерживают 15 векторов прерываний (табл. 12). Младшие пять векторов аналогичны имеющимся во всех контроллерах семейства MCS-51. Шестой вектор обслуживает третий таймер/счетчик (он появился только начиная с кристаллов семейства MCS-52). Седьмой вектор, имеющийся только в 8XC51FX, 8XL51FX и 8XC51GB, поддерживает программируемую матрицу счетчиков (РСА). Последний дополнительно располагает прерываниями от шести внешних входов (INT2-INT6), второй матрицы программируемых счетчиков, АЦП и расширенного последовательного порта. Во всех контроллерах семейства MCS-51 каждое прерывание может быть запрещено установкой в низкий уровень соответствующего бита в регистре IE. Естественно, это справедливо и для 8XC51GB. Однако поскольку он содержит вдвое больше источников прерывания, то для их разрешения/запрещения используется дополнительный регистр IEA (табл. 13). Как и в предыдущем случае, установка бита в единицу приводит к разрешению соответствующего прерывания, сброс в ноль запрещает его. Адрес регистра IEA - 0А7Н.

Таблица 13

Отметим, что все прерывания, в том числе и описанные в табл. 13, могут быть одновременно запрещены установкой в ноль бита ЕА (IE.7) - старшего бита регистра IE. Каждое прерывание может иметь свой собственный приоритет - от уровня О (низшего) до уровня 3 (высшего). Уровень приоритета определяется состоянием битов в регистровых парах IP, IPH и IPA, IPHA. Первая из упомянутых идентична имеющейся в более ранних контроллерах и подробно была описана при рассмотрении группы 8XC51FX. Вторая пара (адреса регистров соответственно 0В8Н и 0В6Н) имеется только у 8XC51GB и обслуживает прерывания, которые есть только у этих контроллеров. В табл. 14 приведено соответствие между битами регистров и прерываниями, уровень которых они определяют.

В табл. 15 приведено тов и состоянием битов соответствие между уровнями в регистровых парах IP, IPH и приорите-IPA, IPHA. Таблица 15

Таблица 16 Прерывания с низким приоритетом могут быть в свою очередь прерваны только событием более высокого приоритета (но не равного). Соответственно прерывание с высшим приоритетом прервано быть не может. Если процессор одновременно получил запросы на два или более прерывания с одинаковым приоритетом, то очередность их обработки определяется специальной последовательностью опроса флагов прерывания. У 8XC51GB эта последовательность выглядит следующим образом (табл. 16). Внешние прерывания INTO и INT1 микроконтроллера 8XC51GB полностью соответствуют аналогичным прерываниям всех микроконтроллеров семейства MCS-51 и могут в зависимости от состояния битов ITO и IT1 регистра TCON фиксироваться как по уровню, так и по перепаду из 1 в 0. Внешние выводы INT2 и INT3 могут реагировать как на положительный, так и на отрицательный фронт сигнала. Микросхема имеет регистр EXICON (0С6Н), содержащий биты IT2 и IT3, он-

ределяющие активный фронт сигнала на выводах P5.2(INT2) и Р5.3( INT3 ). При установке бита 1Тп в О прерывание инициируется по отрицательному фронту, при ITn =1 - по положительному. Внешние события INT4 - INT6 фиксируются только по положительному фронту на выводах Р5.4( INT4 )-Р5.6( INT6). Все внешние прерывания генерируют соответствующие аппаратно устанавливаемые флаги. Для событий INTO, INT1 - это биты IEO и IE1 регистра TCON. Флаги IE2...IE6 находятся в регистре EXICON. Сброс их осуществляется аппаратно в момент перехода процессора на подпрограмму обработки соответствующего прерывания. За время машинного цикла опрос выводов внешних прерываний осуществляется лишь однажды. Поэтому для того, чтобы прерывание было зарегистрировано, длительность его активного уровня должна превышать один машинный цикл (12 периодов тактового генератора). В табл. 17 приведено назначение битов регистра EXICON. Таблица 17

РАСШИРЕННЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ Расширенный последовательный порт (SEP) располагает аппаратными средствами для реализации шины FC-bus, де-факто являющейся стандартом последовательного обмена. SEP допускает функционирование в четырех различньгх режимах, имеет три различньгх источника тактирования. Под его нужды задействовано два вывода микросхемы: Р4.1 - ввод/вывод данных и Р4.0 - для вывода тактирующего сигнала. Передаваемый или принимаемый пакет состоит из восьми бит данных. При этом используется восемь тактов работы SEP. В отсутствие принимаемой или передаваемой информации тактовый сигнал и данные неактивны. За SEP закреплены три SFR-регистра - SEPCON (0D7H), SEPDAT (0Е7Н) и SEPSTAT (0F7H). Регистры адресуются только побайтно. Назначение бит в регистрах SEPCON и SEPSTAT приведено в табл. 18 и 19 соответственно. Таблица 18

Таблица 19

На рис. 10 приведены отличительные особенности режимов работы SEP - активные уровни сигнала тактирования и фронты, используемые для приема или передачи. Как следует из табл. 18, режим работы SEP определяется состоянием битов CLKPOL и CLKPH, расположенных в регистре SEPCON. Для приема или передачи байта пользователь должен установить режим работы порта (биты CLKPOL и CLKPH), скорость передачи StPMODEO Тактовый импульс SEPM0DE1 SEPM0DE2 - Тактовый импульс SEPM0DE3 - rln n rL л ~lJ~u~LriJTJ Защелкивание Данные (SEPS1 и SEPSO), а также установить в 1 бит SEPE. Процесс передачи начинается сразу после загрузки байта в регистр SEPDATA. Прием инициируется установкой в 1 бита SEPREN в случае, ког- ермог.рз-Г LJ L J L I LJ L да регистр SEPDATA пуст и нет передачи. После приема 8 битов SEPREN аппаратно сбрасывается. Завершение р^, приема или передачи приводит к установке в 1 бита SEPIF. Сброс этого бита возможен только программным nyieM. Если пользователь совершит попытку записать или прочитать информацию в регистр SEPDATA в момент передачи или приема, устанавливается соответствуюгций бит ошибки. Флаг SEPFWR устанавливается при наличии такой попытки в процессе передачи байта, а SEPFRD - в процессе приема. Прерывания, связанные с установкой этих битов отсутствуют, вследствие чего пользователь должен контролировать их состояние самостоятельно. Естественно, сброс этих флагов может быть осугцествлен только программным путем. АППАРАТНЫЙ СТОРОЖЕВОЙ ТАЙМЕР Аппаратный сторожевой таймер (HWDT) производит сброс микроконтроллера при своем нереполнении, таким образом являясь средством борьбы с зависанием системы (зацикливанием программы). На выполнение аналогичной функции может быть настроен и таймер-счетчик модуля 4 РСА, но такое его применение ограничивает возможности пользователя, в связи с чем в 8ХС51GB появился самостоятельный WDT, не требующий использования РСА. Аппаратный сторожевой таймер состоит из 14-битного счетчика, инкрементируемого в каждом машинном цикле, и SFR-регистра WDTRST (0А6Н). Таймер всегда активен и при работающем тактовом генераторе непрерывно увеличивает содержимое счетчика. Средств остановки таймера нет. Если программа пользователя не записывает в WDTRST никакой информации, то через каждые 16384 машинных цикла HWDT формирует сигнал RESET, который сбрасывает микроконтроллер. При этом счетчик обнуляется. Для предупреждения срабатывания HWDT пользовательская программа с промежутком не реже 16383 машинных циклов должна заносить в 1 ... 3 4 5 6 7 8 9 ... 20 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |