|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Применение операционных усилителей 1 ... 33 34 35 36 37 38 39 ... 57 Унитарный код в двоичный. - Прим. ред. > И теряет точность. - Прим. ред. состояние своих выходов после приложения Lex. Все компараторы, для которых Ubx < Uon, нс мсняют свосго состояния. ВЫходы компараторов подводятся к декодирующей схеме, которая преобразует совокупность состояний компараторов после приложения Ubx в цифровое слово Параллельные АЦП отличаются быстродействием - время преобразования составляет 30 не. Это объясняется тем, что цифровой выход появляется немедленно по истечении времени установления компараторов и времени прохождения сигналов через декодирующую логическую схему. Однако общее число используемых компараторов составляет 2 - 1, где п - число двоичных разрядов. Таким образом, 8-разрядный параллельный АЦП требует 2* - 1 = 256- 1 =255 компараторов. С увеличением числа разрядов параллельный преобразователь становится очень дорогостоящим Двухразрядный параллельный АЦП со схемой декодирования показан на рис. П.9, б. Опорные напряжения, прикладываемые к компараторам, начинаются от значения Uon. i, равного половине младшего значащего разряда, умноженной на величину полного опорного напряжения, и кончаются значением, определяемым разностью Uon - Uon. ь Так, для двухразрядного параллельного преобразователя опорные напряжения для трех (2-1) компараторов с Uon = 3 В составляют 0,5, 1,5 и 2,5 В. Если Ubx < 0,5 в, то все выходы компараторов имеют низкий уровень напряжения, и цифровой код будет 00. Если 0,5 В Ubx 1,5 в, то выход компаратора / приобретает высокий уровень, а выход компаратора 2 сохраняет низкий. Выход компаратора 2 после инвертирования подается на логическую схему И , выход которой при этом принимает высокий уровень. Таким образом, на выходе логической схемы ИЛИ устанавливается высокий уровень, что приводит к появлению цифрового кода 01. Если входной сигнал лежит в диапазоне 1,5 В Ubx 2,5 В, то выход компаратора 2 приобретает высокий уровень, а выход логической схемы И - низкий. При этом устанавливается цифровой код 10. Если Ubx > 2,5 В, то выходы компараторов 2 и 3 имеют высокий уровень. Выход компаратора 3 при этом обеспечивает на выходе логической схемы ИЛИ в канале младшего разряда высокий уровень напряжения, так что в итоге устанавливается цифровой код 11. АЦП с двухтактным интегрированием. АЦП с двухтактным интегрированием (двойным наклоном) представляет один из нескольких типов схем интегрирующих преобразователей. Интегрирующие преобразователи отличаются малым быстродейст-ием (их время преобразования составляет от 20 до 40 мс) и НИЗКОЙ стоимостью; как правило, они очень точны и линейны. Они используются в цифровых вольтметрах, измерительных приборах с цифровой индикацией (digital panel meters) и системах сбора данных в тех случаях, когда скорость преобразования не является решающим фактором. Схема АЦП с двойным наклоном, приведенная на рис. 11.10, является наиболее популярной схемой интегрирующих АЦП. Она обеспечивает высокую точность и требует только кратковременной стабильности задатчика времени, в то же время хорошо подавляет шумы на входе. Работу схемы можно понять, если обратиться к рис. 11.10. Преобразование начинается с установки счетчика на нуль с помощью управляющей логики. Ключ Кл1 устанавливается в положение, при котором к интегратору присоединено [/вх, и счетчик начинает считать импульсы задатчика времени. В то время когда счетчик считает импульсы времени, t/sx (если оно положительно) вызывает нарастание отрицательного выходного напряжения интегратора со скоростью, пропорциональной (Увх- в момент ti появления сигнала переполнения счетчика выходное напряжение интегратора будет Ц1/2)МЗР  7R i  Т ;  2 -о 2 -О ЦИФРОВОЙ

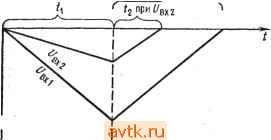

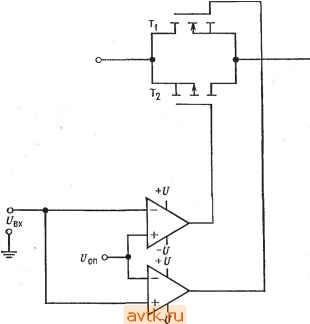

Рис. 11.9. Параллельный аналого-цифровой преобразователь. ( - общая схема параллельного преобразования, 1/,!,-напряжение на входе, соответствующее полной шкале; б - двухразрядный параллельный АЦП с декодирующей логической схемой. В момент появления сигнала переполнения счетчика ключ Кл1 переключается на напряжение -Uon, а счетчик после сброса в нуль начинает считать снова Интегрирующий конденсатор начинает разряжаться с постоянной скоростью, пропорциональной величине -Uon/RC. Когда конденсатор интегратора разрядится до нуля, компаратор останавливает счетчик. Содержимое счетчика при фиксированном ty представляет отнощение Uex/Uon- Действительно, из условия равенства нулю напряжения на выходе интегратора в момент t2 имеем f/вых (2) = f/вых ih) - {-U0J2IRC) =0, где f/вых (/l) = -f/Bxl ?C или f/Bx/f/on = Сброс счетчика в нуль организовывать специально не надо - при пе-Реролнении он как раз и обнулится . - Ярйж. ред. с on -J С Задатчик времени  Схема управления 1 f Счетчик о о 6 6 о (10 Цифровой выход а  -о ibix Y, вых.макс -  Рис. 11.10. Аналого-цифровой преобразователь с двухтактным интегрированием. о - блок-схема. У, - интегратор, Уа - компаратор; б - выход интегратора при £/bXi>1/bx2, скорость заряда на интервале фиксирована с помощью I/qj меняется с изменением 1/ скорость заряда при фиксированном ti из меняется с U, V макс ~ напряжение, соответечвующее полной шкале усилителей. > Соответственно для 50 Гц промышленной частоты интервал времени <1 надо брать равным 20 мс. - Прим. ред. 2> Основной недостаток этого метода тот же, что и у параллельных АЦП, - неравномерность ступеней, или каналов , преобразования. - Ярмлг, ред. Отсюда следует, что задатчик времени должен быть стабильным только в интервале времени ti 2- Подавление помех получается в результате того, что на большом интервале времени усредненное напряжение помех приближается к нулю. Если = 16,67 мс, как это часто выбирают, то всегда присутствующая помеха 60 Гц очень хорошо подавляется ). АЦП с двойным наклоном и другие интегрирующие АЦП имеются как в монолитном, так и в гибридном интегральном исполнении. АЦП с последовательной аппроксимацией (с поразрядным кодированием). Поразрядное взвешивание является наиболее популярным (распространенным) методом аналого-цифрового преобразования. Эти схемы имеют умеренную стоимость, обеспечивают скорость преобразования в пределах от умеренной до высокой и хорошую точность. Для п-разрядного преобразователя преобразование аналогового напряжения в число требует п временных тактов ). Преобразователь состоит из источника опорного напряжения, задатчика времени (тактовых импульсов), ЦАП, компаратора и регистра последовательных приближений (имеется в виде интегральной схемы). Регистр последовательных приближений (РПП) состоит из регистра хранения, регистра сдвига и соответствующей управляющей логики. Блок-схема регистра последовательных приближений показана на рис. 11.11, а, а выходной сигнал ЦАП - на рис. 11.11, б. Преобразование начинается с установки 1 в старший разряд регистра хранения и О во все остальные. ЦАП преобразует старший разряд в аналоговое напряжение, равное Д^/макс (половине полной шкалы аналогового напряжения). Компаратор сравнивает выход ЦАП с аналоговым входным напряжением. Если входное напряжение больше, чем выходное ЦАП, то в ячейке старшего разряда сохраняется 1 , в противном случае в этой ячейке устанавливается О . Регистр сдвига в начале следующего временного такта сдвигает 1 в следующий младший разряд. Если выходное напряжение ЦАП при этом меньше чем Ubx, то в слсдующсм разряде устанавливается 1 , в противном случае в следующем разряде устанавливается О . Процесс продолжается до тех пор, пока не будут проверены все разряды.  < ЦАП Задатчик времени Управляющая схема Регистр хранения Регистр сдвига £макс 10110101 вып. ЦАП 8 ut Рис. II.II. Аналого-цифровые преобразователи с последовательной аппроксимацией. о - блок-схема; б-форма выходного напряжения ЦАП, u -фиксированное вначе- ние входного напряжения, преобразуемого в цифровой код 10110101; Д< -период тактовых импульсов. Если Ugjj цап<вх- старшем разряде устанавливается 1 . если £/bj j; цап>/вХ старшем разряде устанавливается о . > Как раз в ЦАП и АЦП часто применяют биполярные коммутаторы тока. Полевые ключи используют обычно для коммутации переменных аналоговых сигналов. - Прим. ред. Точность АЦП последовательных приближений не может быть выше точности используемого в нем ЦАП, а обычно одна существенно меньше. Напомним еще раз, что эти преобразователи выпускаются в виде интегральных схем. 11.1.6. АНАЛОГОВЫЕ ключи Необходимость выполнять коммутационные функции в кристаллах интегральных схем преобразователя, а также необходимость в ключах, совместимых с интегральной технологией, привели к развитию интегральных схем ключей. Интегральные схемы аналоговых ключей имеются как в виде отдельных кристаллов, так и в виде непосредственно встроенных во многие аналого-цифровые и цифро-аналоговые интегральные схемы'). Коммутирующими элементами служат диффузионные или МОП-транзисторы. Эти ключи отличаются значительно большим быстродействием по сравнению с электромеханическими, но в отличие от последних они не предназначены для коммутации больших токов или напряжений. Типичный аналоговый ключ на диффузионном полевом транзисторе фирмы National Semiconductor АНО140 показан на рис. 11.12. Спецификации на всю серию АНО120, АНО130, АНО140, АНО150 приведены в приложении В. Особенности этой серии заключаются в том, что время включения (замыкания) доведено до 0,4 мкс, а время выключения (размыкания) - до 1 мкс. Сопротивление во включенном состоянии может иметь пять значений в диапазоне между 10 и 80 Ом (в зависимости от типа ключа). В серии предусмотрена работа с высоким (гЫО В) и низким (±7,5 В) входными напряжениями. Ключи работают с напряжением питания управления ±15 В, но могут переключаться с помощью ТТЛ-логики. Для переключения ключа схема его управления требует перепада только 2,5 В при 0,1 мА. Ключи могут коммутировать токи вплоть до 30 мА. Для того чтобы обеспечить замыкание ключа, выполненного на диффузионных полевых транзисторах, необходимо иметь напряжение стока выше напряжения остальных электродов, что может рассматриваться как недостаток. Схема, приведенная на рис. 11.12, а работает следующим образом: ключ приводится в действие заземлением разрешающего входа. Если этот вход имеет высокий потенциал, равный нулю, принятому для логической 1 , то входные транзисторы Tl не могут открыться и ключ лишен возможности включиться. Разреш. Разреш.   Рис.-11.12. Аналоговый ключ на диффузионных полевых транзисторах фирмы National- Semiconductor АН0140. (С разрешения фирмы National Semicenductor Corp.) в - схема сдвоеииого однополюсного ключа на одно направление; б - блок-схема интегральной схемы. С- сток, И - исток. Если разрешающий вход имеет низкий потенциал, то при t/вх > 2,5 В транзисторы Ti отпираются, что в свою очередь приводит к отпиранию транзисторов Т2, и запиранию транзистора Тл- Напряжение затвора диффузионного полевого транзистора теперь равно напряжению в канале полевого транзистора контакт ключа  кентакт ключа Рис. 11.13. Схема аналогового ключа на МОП-транзисторах. &з^>1дп, ключ включен, (U,), -Ц/, (3)2- = -U; texon о 1 ° и остается выще напряжения источника сигнала. Когда Ubk 0,8 В, то Tl и Т2 закрываются и открывается Т4. Транзистор Т4 через прямо смещенный коллекторный переход Тз присоединяет затвор канального полевого транзистора к -U и тем самым удерживает его в закрытом состоянии. Эмиттерный переход Гз при этом закрыт. Интегральные схемы ключей на МОП-транзисторах могут быть построены так, что при этом будет безразлично, какой из контактов присоединен к напряжению высокого уровня. Как показано на рис. 11.13, аналоговый ключ на МОП-транзисторах , состоит из параллельного соединения транзисторов с р- и п-ка-налами. Два усилителя обеспечивают надлежащее согласование полярности управляющего напряжения и напряжений, прикладываемых к затворам. Когда Ubx <. Uon, В схсмс рис. 11.13 затвор канала /г-МОП-транзистора Ту находится под напряжением -U, а затвор канала р транзистора Т2 - под напряжением -\-U. При этом ключ разомкнут при любых напряжениях на его контактах в пределах напряжения источника питания. Когда Ubx > Uon, затвор канала-МОП-транзистора получает напряжение +U, а затвор канала р получает -U. Ключ теперь замкнут при любых напряжениях на контактах, лежащих в пределах от напряжения положительного источника питания минус пороговое напряжение п-МОП-транзистора и до напряжения отрицательного источника питания минус (отрицательное) пороговое напряжение р-МОП-транзистора. Интегральные схемы ключей выпускаются различными производителями полупроводниковых приборов. 11.1.7. КОММУТИРУЕМЫЕ КОНДЕНСАТОРЫ Появление надежных аналоговых ключей на МОП-транзисторах, изготовляемых в виде интегральных схем, позволяет конструкторам интегральных схем использовать малые и точные по величине отнощения емкостей МОП-конденсаторы в сочетании с аналоговыми, ключами для выполнения функций, которые прежде требовали резисторов. МОП-конденсаторы и меньще по размерам, и значение их емкости более точно устанавливается по сравнению со значениями сопротивлений резисторов в монолитных интегральных схемах. Два применения коммутируемых конденсаторов составляют компараторы и устройства установки коэффицеинта усиления. Компаратор с коммутируемым конденсатором. На рис. 11.14 показан компаратор с коммутируемым конденсатором, или, как его иначе называют, компаратор, балансирующий заряд. Он используется в монолитных интегральных МЦП фирмы National Semiconductor. Схема работает за счет поочередной выборки опорного и входного напряжений. Когда Кл, замкнут. Су и Сг заряжаются до Uon. Во время заряда конденсаторов усилитель шунтирован ключом. Затем Кл1 размыкается и Клг замыкается. Если Ubx = Uon, никакого изменения зарядов на конденсаторах не происходит. Если Ubx < Uon, то выходное напряжение усилителя получит положительное отклонение, при Ubx > Uon - отрицательное. Отклонение выходного напряжения передается с помощью связи по переменному току через конденсатор Сс к триггеру с импульсной установкой. Отклонение выходного напряжения определяется произведением изменения напряжения на конден- 1 ... 33 34 35 36 37 38 39 ... 57 |

||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |