|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Системы передачи данных 1 2 3 4 5 6 7 8 ... 38 Рис. 3.9. Регистры делителя скорости передачи 7 6 5 4 3 2 1 0

Делитель скорости передачи (старший байт)

Делитель скорости передачи (младший байт) Таблица 3.3. Общепринятые делители скорости передачи Скорость передачи в бодах Делитель (для 16-фазвого синхронизирующего сигнала)

* Реальная скорость на 0,026% больше Делитель скорости передачи записывается в микросхеме 8250 в виде двух байтов: старшего байта и младшего байта. Этот 16-разрядный делитель хранится в двух внутренних 8-разрядных регистрах-защелках. При загрузке одного байта в каждый из этих регистров загружается весь 16-разрядный делитель. Это просто озна чает, что, комплектуя полный делитель, процессор может записывать эти байты в УАПП в любом порядке. Формат регистров делителя скорости передачи показан на рис. 3.9. Два 8-разрядных регистра, образующих составной регистр делителя скорости передачи микросхемы 8250, не имеют собственных адресов в УАПП. Они адресуются как УАПП-регистры О (младший байт) и 1 (старший байт), т. е. точно так же, как регистр хранения передатчика и регистр разрешения прерывания. Для того чтобы определить. какая пара внутренних регистров должна получить данные, УАПП проверяет значение разряда 7 регистра управления линией. Только в том случае, когда в этом разраде, называемом разрядом доступа к регистрам делителя скорости передачи (DLAB), находится 1, данные, записываемые в УАПП, направляются в регистры делителя скорости передачи. Если DLAB = О, данные обычным образом направляются в РХП и РРП. Таким образом, для загрузки регистров делителя скорости передачи необходимо выполнить следующие операции. 1. Записать 1 в разряд 7 (DLAB) РУЛ. 2. Записать 16-разрядный делитель в УАПП-регистры О и 1. 3. Записать О в разряд 7 (DLAB) РУЛ. Регистр сверхоперативной памяти, РСП (SCR). В микросхеме 8250 имеется один дополнительный 8-разр51Дный регистр, называемый регистром сверхоперативной памяти (РСП). Этот регистр, используемый как для записи, так и для считывания информации, адресуется как УАПП-регистр 7. Необычность этого регистра заключается в том, что он не оказывает абсолютно никакого влияния на работу УАПП. Этот регистр предназначен для использования программистом в качестве запоминающего устройства для временного хранения данных. Если вы решили использовать этот регистр, не забудьте, что и другие программисты могут принять точно такое же решение. Информация, записываемая в этот регистр одной программой, не защищена от возможной перезаписи какой-либо другой программой. Этот регистр отсутствует в ранних вариантах микросхемы 8250. Формат РСП показан на рис. 3.10. Рис. 3.10. Регистр сверхоперативной памяти (РСП) Информационные разряды УАПП 16550 Микрсюхема 8250 значительно упрощала программирование систем последовательной связи. Работая со скоростями до 9600 бод, она выполняла свои функции превосходно, полностью соответствуя по своим характеристикам невысокому (в прошлом) быстродействию IBM PC. Но, несмотря на столь успешное применение в прошлом и почти универсальную популярность, на сегодняшнем уровне техники связи с ее исключительно высокими скоростями передачи информации и многозадачными рабочими системами микросхема 8250 выглядит весьма посредственно. Чтобы исправить ситуацию, фирма National разработала и выпустила микросхему PC16550C/NS16550AF - улучшенную модификацию исходного УАПП типа 8250. По умолчанию микросхема 16550 эмулирует микросхему 8250 и в большинстве случаев может быть установлена на месте последней. Работая в совместимом режиме, эта микросхема является полным функциональным аналогом УАПП 8250 и 16450. Рассматривая УАПП 16550, разумно принять во внимание те сведения, которые изложены ранее в этой главе при обсуждении УАПП 8250. Поэтому ниже подробно описываются только новые возможности и режимы работы микросхемы 16550. В отличие от микросхемы 8250, микросхема 16550 имеет второй режим работы, предназначенный для сокращения вмешательства процессора в процедуру последовательной передачи данных. В этом режиме внутренние буферные регистры приемника и передатчика расширяются от 1 до 16 байтов и управляются с использованием логики первым пришел - первым вышел , или FIFO-логики (First In, First Out). FIFO-буфер приемника используется также для хранения трех битов информации об ошибках для каждого символа. Ошибки четности, кадрирования и ВКБАК-сигналы буферизуются вместе с символом, к которому они относятся. Характеристики и функциональные возможности Микросхема 16550 совместима снизу вверх с микросхемами 8250 и 16450. Поэтому она обладает более широким набором характеристик и функциональных возможностей по сравнению с последними. Микросхема 16550 выполняет следующие функции. Обеспечивает простой интерфейс между РС-шиной адреса/данных и модемом или другим внешним устройством. Автоматически добавляет, удаляет и проверяет кадрирующие биты. I Генерирует и проверяет биты четности под управлением специальной программы. I Выделяет указатели состояния операций передачи и приема, а также состояния линии передачи данных и устройства сопряжения. Содержит встроенные сдвиговые регистры и регистры хранения для операций передачи и приема данных, что исключает необходимость точной синхронизации работы процессора с потоком последовательных данных. Содержит программируемый генератор-контроллер скорости передачи, работающий с внешним опорным сигналом частотой до 24 МГц. Содержит логические схемы обработки сигналов управления модемом, связанные с системой прерываний. Содержит встроенные средства самотестирования. Может работать под управлением программного обеспечения, разработанного для микросхем 8250 и 16450. Внутренние буферы позволяют хранить до 16 символов (и связанную с ними информацию об ошибках) при операциях передачи и приема данных. Блок-схема В своей основе УАПП 16550 - это улучшенная модификация УАПП 8250. Поэтому внутренняя конфигурация микросхемы 16550 очень близка к конфигурации микросхемы 8250 и может быть представлена как совокупность схем синхронизации, логических схем управления и коммутации сигналов, буферов и 12 адресуемых регистров. Упрощенная блок-схема УАПП 16550 изображена на рис. 3.11. На этой блок-схеме указаны взаимосвязи между отдельными структурными единицами и типичные сигналы на входах и выходах микросхемы. Микросхема 16550 монтируется в том же корпусе, что и микросхема 8250. Два вывода, однако, переопределены для реализации процедуры прямого доступа к памяти (ПДП). В микросхеме 8250 вывод CSOUT обеспечивает обратную связь с системой, которая выбрала данную микросхему и готова для передачи данных. В микросхеме 16550 этот вывод прдназначен для выдачи сигнала TXRDY. Когда в буфере передатчика нет никаких символов, этот сигнал имеет низкий уровень. TXRDY-сигнал остается в этом состоянии до тех пор, пока не заполнится буфер передатчика. Влияние такого переопределения данного вывода минимально, так как в стандартной реализации по- Рис. 3.11. Блок-схема УАПП 16550 ПК-интерфейс Внутренняя Коммуникационный интерфейс шина данных УАПП D7-D0 Данные Буфер шины данных Регистр разрешения прерываний INTR Схема управления прерываниями Регистр йвода-БЫйода прерываний Регистр сверхоперативной намети выбора кристалла . . 8. Л Схема А2-А0 <=Щ> выбора регистра WR WRC=S Схемы выборе режима записи/ считывания и упряалвкия  FIFO-буфер приемника Буферный регистр приемника

-DTR ►0UT1 6РТ2 -DSR -CTS -DCD  Сдвигающий регистр приемника -SIN

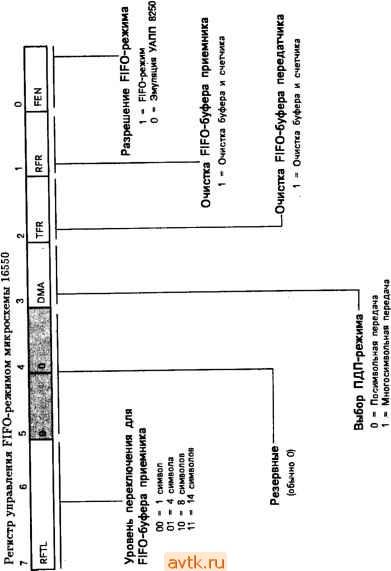

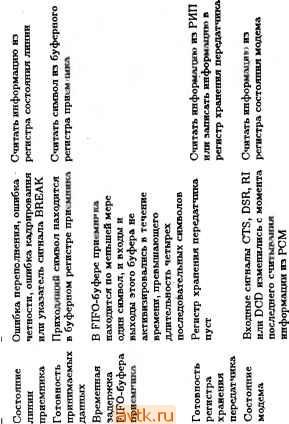

-BAUDOUT Регистр управления FIFO-режимом и -SOUT Генератор опорного синхросигнала УАПП (24 МГц мэ с.) т следовательного порта IBM PC с использованием микросхемы 8250 этот вывод никуда не подключается. Микросхема 16550 вырабатывает также один дополнительный сигнал для указания состояния буфера приемника. Этот RXRDY-сигнал имеет низкий уровнь, если в буфере приемника находится хотя бы один символ. Низкий уровень RXRDY-сигнала сохраняется до тех пор, пока буфер приемника не будет пуст. Влияние этой замены также минимально, поскольку соответствующий вывод микросхемы 8250 никуда не подключается. Описания регистров Определения большинства полей-разрядов регистров микросхемы 16550 идентичны с определениями соответствующих разрядов регистров микросхемы 8250 как в режиме эмуляции УАПП 8250, так и в FIFO-режиме. Для перечисленных ниже регистров УАПП 16550 описания не приводятся, поскольку все детали можно найти в приведенных ранее описаниях регистров микросхемы 8250. Регистр хранения передатчика (РХП) Буферный регистр приемника (БРП) Регистр управления линией (РУЛ) Регистры делителя скорости передачи Регистр сверхоперативной памяти (РСП) Регистр управления модемом (РУМ) Регистр состояния модема (РСМ) Для обеспечения работы УАПП в FIFO-режиме микросхема 16550 содержит один новый регистр, и расширены возможности некоторых уже известных нам регистров. Эти изменения описываются ниже. Регистр управления FIFO-режимом (FCR). Этот регистр разбит на шесть полей. Записывая в него определенную информацию, можно разрешать или запрещать доступ к FIFO-буферам и очищать эти буферы. Этот регистр обеспечивает также управление ПДП-сигналами, вырабатываемыми микросхемой, и уровнем переключения для FIFO-прерывания приемника. Регистр управления FIFO-режимом предназначен только для за писи и адресуется как УАПП-регистр 2 (такой же адрес в УАПП имеет РИП). Все поля регистра должны программироваться после предва рительной установки 1 в разряде 0. Формат регистра управления FIFO-режимом показан на рис. S.12. Назначение каждого из полей этого регистра объясняется ниже.  М 1. Разряд 0: разрешение FIFO-режима (FEN). Установка этого поля в 1 разрешает доступ к FIFO-буферам передатчика и приемника. Сброс этого поля в О выводит микросхему 16550 из FIFO-режима и возвращает ее в режим эмуляции УАПП 8250. Изменение значения данного разрада приводит к очистке FIFO-буферов передатчика и приемника, БРП и РХП. Однако на сдвиговые регистры передатчика и приемника это изменение не влияет. Данное поле выполняет также функцию защелки доступа к остальным полям регистра. Запись какой-либо информации в эти поля возможна только при установке разряда разрешения FIFO-режима в 1; в противном случае эта информация не попадает в регистр. 2. Разряд 1: очистка FIFO-буфера приемника (RER). Это поле выполняет свои функции только в FIFO-режиме. Запись 1 в это поле приводит к очистке всех байтов FIFO-буфера приемника и к начальной установке (в 0) счетчика символов для FIFO-процедуры. Заметим, однако, что эта операция не влияет на любой необработанный символ, который формируется в сдвиговом регистре приемника. Нет необходимости осуществлять вручную очистку данного разряда; он автоматически сбрасывается в О по завершении операции инициализации. 3. Разряд 2: очистка FIFO-буфера передатчика (TFR). Это поле выполняет свои функции только в FIFO-режиме. Запись 1 в это поле приводит к очистке всех байтов FIFO-буфера передатчика и к начальной установке (в 0) счетчика символов для FIFO-процедуры. Заметим, однако, что эта операция не влияет на любой текущий символ, передаваемый из сдвигового регистра передатчика. Нет необходимости осуществлять вручную очистку данного разряда; он автомат тически сбрасывается в О по завершении операции инициализации. 4. Разряд 3: выбор ПДП-режима (DMA). Установка этого поля определяет логику управления сигналами, присутствующими на выводах RXRDY и TXRDY микросхемы. Запись О в это поле обеспечивает выбор ПДП-режима О и разрешает посимвольную ПДП-передачу данных. Этот ПДП-режим возможен как в режиме эмуляции микросхемы 8250, так и в FIFO-режиме. В ПДП-режиме О, если в БРП (режим эмуляции УАПП 8250) или в FIFO-буфере приёмника (FIFO-режим) находится хотя бы один символ, то на выводе RXRDY микросхемы действует активный (низкий) уровень сигнала. Этот вывод остается в активном состоянии до полной очистки БРП или FIFO-буфера приемника. В ПДП-режиме О, если в РХП (режим эмуляции УАПП 8250) или в FIFO-буфере передатчика (FIFO-режим) нет ни одного символа, то на выводе TXRDY микросхемы действует активный (низкий) уровень сигнала. Этот вывод переходит в неактивное состояние, когда первый символ загружается в РХП или FIFO-буфер передатчика. Установка поля выбора ПДП-режима в 1 инициирует выбор ПДП-режима 1 и возможна только в том случае, когда микросхема 16550 находится в FIFO-режиме. ПДП-режим 1 обеспечивает многосимвольную передачу данных, когда символы передаются один за другим до полной очистки FIFO-буфера приемника или до полного заполнения FIFO-буфера передатчика. В ПДП-режиме 1 вывод RXRDY микросхемы переключг1ется в активное состояние (низкий уровень), когда число символов в FIFO-буфере приемника достигает уровня переключения или символы находятся в этом буфере дольше определенного промежутка времени (см. ниже). Активное состояние RXRDY-сигнала сохраняется до полной очистки FIFO-буфера приемника. В ПДП-режиме 1, если в FIFO-буфере передатчика (FIFO-режим) нет ни одного символа, то вывод TXRDY микросхемы переключается в активное состояние (низкий уровень). Активное состояние TXRDY-сигнала сохраняется до полной загрузки FIFO-буфера передатчика. 5. Разряды 5-4: резервные. Эти два разряда считаются резервными для использования в будущем. Как и в микросхеме 8250, в эти разряды обычно записывается логический 0. 6. Разряды 7-6: уровень переключения дл.я FIFO-буфера приемника (RFTL). Содержимое этих двух полей определяет число символов, которые должны находиться в FIFO-буфере приемника, прежде чем будет генерироваться прерывание по состоянию этого буфера. Возможные уровни переключения и установки разрядов, необходимые для выбора этих уровней, приведены ниже. Разряд 7 Разряд 6 Уровень переключения 0 0 1 символ 0 14 символа 10 8 символов 1 1 14 символов Регистр состояния линии, РСЛ (LSR). Содержимое отдельных полей этого регистра указывает текущее состояние процесса переда чи данных. Формат РСЛ в микросхеме 16550 показан на рис. 3.13. Новые определения полей в разрядах 1 и 7 РСЛ приведены ниже. Функциональное назначение других полей регистра остается таким же, как в микросхеме 8250. 1. Разряд 1: ошибка переполнения (ОЕ). Логические схемы приемника в микросхеме 16550 работают непрерывно. Символы принимаются, собираются в сдвиговом регистре приемника и передаются в БРП или FIFO-буфер в зависимости от режима работы микросхемы. В режиме эмуляции УАПП 8250 символ, который полностью собран, будет записываться в БРП, разрушая находящийся там несчитанный символ. В FIFO-режиме микросхема работает по-другому. Если FIFO-буфер заполнен сверх уровня переключения, ошибка переполнения имеет место, когда FIFO-буфер заполнен целиком, а следующий символ полностью собран в сдвиговом регистре приемника. Ошибки переполнения не накапливаются, а только фиксируются в РСЛ при своем появлении. Символ, находящийся в сдвиговом регистре, не за писывается в FIFO-буфер. Следующий принимаемый символ будет разрушать предыдущий символ в сдвиговом регистре примника, а не в FIFO-буфере. Разряд ошибки переполнения автоматически сбрасывается в О , когда процессор считывает информацию из РСЛ. 2. Разряд 7: ошибка в FIFO-буфере приемника (RFE). В режиме эмуляции УАПП 8250 в этом разряде постоянно записан 0. В FIFO-режиме данный разряд устанавливается в 1 при'появлении ошибки четности, кадрирования или сигнала BREAK, которые связаны с одним или несколькими символами в FIFO-буфере приемника. Сообщение об ошибке передается в другие поля регистра, когда соответствующий символ с ошибкой становится следующим символом, который должен быть считан из FIFO-буфера. Заметим, что при работе микросхемы 16550 в FIFO-режиме существуют ограничения на операции записи в регистр управления FIFO-режимом. Для того чтобы загрузить байт данных в FIFO-буфер приемника, символ должен быть записан с использованием петлевой конфигурации микросхемы. В любом случае запись в разряды О и 7 запрещена, пока установлен FIFO-режим. Регистр разрешения прерываний, РРП (IER). Регистр разрешения прерываний используется для разрешения и запрещения по отдельности четырех типов прерываний, которые может генерировать микросхема 16550. Когда возникает ситуация, соответствующая разрешенному прерыванию, сообщение о ней передается в регистр идентификации прерываний. Формат этого регистра в микросхеме 16550 в основном идентичен его формату в УАПП 8250 (рис. 3.7). Однако, как видно из следующего определения, в FIFO-режиме функции разряда О расширены. о ю ю м 5 о о. о 0) Z с - (В ю о е  О Ш Э О - s si i о X и Разряд 0: разрешение прерывания из-за временной задержки FIFO-буфера приемника. В FIFO-режиме установка этого разряда в 1 разрешает прерывание по причине временной задержки в работе FIFO-буфера приемника. Если это прерывание разрешено, то оно будет происходить при одновременном выполнении следующих условий. Хотя бы один символ находится в FIFO-буфере приемника. Текущий символ не принят за время, превышающее длительность четырех непрерывно следующих друг за другом символов. Информация из FIFO-буфера приемника не считывалась процессором в течение времени, превышающего длительность четырех непрерывно следующих друг за другом символов. Длительность символа измеряется числом синхронизирующих импульсов контроллералгенератора скорости передачи, так что пороговый уровень задержки не зависит от скорости передачи. Если условия этого прерывания не реализуются, то таймер задержки сбрасывается в исходное состояние каждый раз, когда символ принимается или считывается из FIFO-буфера приемника. Регистр идентификации прерываний, РИП (IIR). Микросхема 16550 - так же, как и 8250 - генерирует в приоритетном порядке четыре типа прерываний. При возникновении ситуации, соответствующей более чем одному прерыванию, в РИП сообщается только о прерывании с наивысшим приоритетом. В режиме эмуляции УАПП 8250 этот регистр выполняет те же функции, что и в микросхеме 8250 (см. описание этого регистра выше в данной главе). При работе микросхемы 16550 в FIFO-режиме в РИП дополнительно определяются два новых поля и одно новое условие прерывания, о котором выдается сообщение. Четыре уровня прерываний перечислены ниже в порядке убывания их приоритетов. Состояние линии приемника (наивысший приоритет) Готовность принимаемых данных или временная задержка FIFO-буфера приемника Готовность регистра хранения передатчика Состояние модема (наинизший приоритет) РИП адресуется как УАПП-регистр 2 и используется только для считывания информации. Формат РИП в микросхеме 16550 показан на рис. 3.14. Назначение новых полей в разрядах 3, 6 и 7 этого регистра объясняется ниже. Функциональное назначение остальных полей регистра такое же, как в микросхеме 8250 (см. выше). Разряды 3-1: поле идентификации прерывания. Если в поле отложенных прерываний (разряд 0) находится логический О, содержимое поля идентификации прерывания указывает отложенное прерывание с наивысшим приоритетом. Возможные прерывания, их приоритеты, типы, причины, а также действия, которые необходимо выполнить для их сброса, указаны в табл. 3.4. Разряды 7-6: флаг разрешения FIFO-режима. Если записать 1 в разряд О регистра управления FIFO-режимом, происходит переключение в FIFO-режим и микросхема 16550 устанавливает это поле в lib. В микросхемах 8250 и 16450 эти два разряда определялись как неиспользуемые разряды с постоянными нулевыми значениями. Поэтому при работе микросхемы 16550 в режиме эмуляции УАПП 8250, это поле сбрасывается в 00 для совместимости. Контроллеры последовательного порта на системной плате персонального компьютера IBM PS/2 используют эти два разряда для самоидентификации в соответствии с табл. 3.5. Контроллер типа 1 эквивалентен асинхронному адаптеру на основе УАПП 8250. Контроллер типа 2 использует УАПП, эквивалентный микросхеме 16550, и обеспечивает поддержку FIFO-режима. Контроллер типа 3 поддерживает как FIFO-режим, так и режим ПДП, которые возможны при использовании УАПП 16550. Заметим, что наличие дефекта в некоторых контроллерах типа 2 на системной плате компьютера PS/2 Model 55 приводит к тому, что разряд 6 РИП не устанавливается в 1 при переходе в FIFO-режим. Попытка использования флагов FIFO-режима для идентификации этого контроллера не позволит выявить возможность поддержки FIFO-процедуры. Независимо от типа контроллера, система PS/2 Model 50 не поддерживает FIFO-режим. Идентификация УАПП К счастью для программистов, УАПП обеспечивает один из самых гибких программируемых интерфейсов для ПК. Например, с точки зрения программиста, микросхемы УАПП 8250 и 16450 совершенно неразличимы. Однако появление микросхемы 16550 несколько изменило ситуацию. Это верно, что микросхема 16550, работая в режиме эмуляции микросхемы 8250, неотличима от последней. Но ее применение не дает никаких гарантий, что она работает именно в этом режиме, когда получает управление. Аппаратная реализация ПК может быть какой угодно, поэтому не стоит удивляться, если обнаружится, что в одном компьютере установлена комбинация УАПП 8250/16450 и 16550. Но прежде чем та о (в и ж S а а а § к о 5 Ж а XI в) о ° с: п -4) 2 < О- ? i n 5 о о X g oi-i ч II II II §1 Z га О) ы П О) с га о Ш u. ;р о о 0> Is S т щ со ш п а а. 3 ОюО и. ей, о. га X б> (О  Таблица 3.5. Идентификация типа последовательного контроллера на системной плате компьютера IBM PS/2 Флаги FIFO-режима Разряд 7 Разряд 6 Тип последовательного контроллера

или иная программа начнет использовать аппаратные преимущества микросхемы 16550 или настроится на работу с микросхемой 8250, необходимо определить тип УАПП, установленного в компьютере. Утилита UARTID, листинг которой на ассемблере приведен ниже (Листинг 3.1), определяет тип установленных в системе УАПП. Листинг 3.1. Утилита UARTID.ASM UARTID.ASM - Identify the installed UARTs From: PC Magazine Progrалтег's Technical Reference Data and Fax Comraunications Robert L. Hummel To create an executable version of this program, use the folloRing commands: HASH UARTID; LIBK UARTID; EXE2BIB UARTID.EXE UARTID.COM DEL UARTID.EXE This demonstration program examines only those ports identified by the BIOS. The BIOS in some systems Hont locate the ports at СОИЗ and С0И4. If you prefer, you can hard-code the search for the folloning standart addresses: С0И1 3F8H С0И2 2F8H C0K3 3E8H С0И4 2E8H CSEG SEGHEBT PARA PUBLIC CODE ASSUHE CS:CSEG, DS:CSEG, ES:CSEG, SS:CSEG lOOH ;СОИ file format This routine determines the type of the UARTs loc&ted by the BIOS. An explanation is then displayed on the console. ИА1В PROC BEAR ASSUHE CS:CSEO, DSiCSEG, ES:CSEG, SS:CSEC MOV DX,OFFSET PROGID$ CALL PRIBT$ ;A11 str ops forvard ;Display program info Retrieve the base addresses of the installed UARTs from the BIOS date area. SUB AX,AX HOV ES.AX ASSUHE ES:BOTHIBG HOV SI,400H CX,4 ;Clear AX ;Point to low memory ;Point to data area ;Examine 4 addresses Loop through the 4 possible base addresses and display the installed devices. HAIB.l: HOV DK,OFFSET UARTIS$ CALL PRIBTS$ LODS WORD PTR ES:[SI] OR AX,AX JBZ HAIB 2 ;Start message ;Get base address ;0 = not installed If the base address is 0, no UART is present. HOV JHP DX,OFFSET BOBE$ SHORT HAIB 3 ;Say not there Test the UART at the base address by attempting to turn on FIFO mode. If the FIFO mode flags are not set, the chip is an 8250/16450. Some of IBH PS/2 Hodel SS systems dont set bit 6 of the IIR correctly Hhen switched to FIFO mode. These serial ports wont be identified as having FIFO capability. HAIB 2: HOV ADD DX.AX DX,2 AL,1 DX.AL ;Put base adr in DX ;DX -> IIR/FCR ;Enable FIFO :Urite to FCR HAII 3:

Increament the UART in the string and loop for remaining ports. lie BYTE PTR [UARTIUH] ;Change ASCII char LOOP HAII.l AX,4C00H 21H ;Terminate program jthru DOS HAII EIDP All program data appears here. PROOID$ UARTIS$ UARTIUH U8250$ 016550$ BOBE$ DB OARTID 1.0 , 254. Robert L. Hummel , 13. DB 10. PC Hagazine Programmers Technical DB References . 13. 10. Data and Fax DB Communications . 13,10 DB 10. $ DB OART DB 1 is $ DB an 8250/16450. , 13. 10. $ DB a 16550. , 13, 10. DB not present. , 13, 10, $ This routine simply uses the DOS Print String function to display a message on the console and is included only to clarify the appearance of the HAII proc. It is assumed that the string offset is passed in the DX register relative to the DS segment. PRIBT$ PROC BEAR ASSUME CSrCSEG, DS:BOTHIBG, EStlOTHIBG. SS:BOTHIBG HOV AH,9 IBT 21H RET PRIIT$ EIDP 108 CSEG EIDS EID HAII Программа UARTID использует регистр управления FIFO-режимом и регистр идентификации прерываний для определения типа установленного УАПП. Если идентифицируемый УАПП является микросхемой 16550, то запись 1 в разряд О регистра управления FIFO-режимом активизирует FIFO-буферы и устанавливает один или оба разряда 7 и 6 регистра идентификации прерываний в 1. Если нет - оба эти разряда будут установлены в 0. Программа UARTID проверяет реакцию УАПП на эту операцию и выдает тип УАПП. Глава 4 Интерфейс RS-232 и последовательный порт в главе 3 описывались возможности УАПП как диспетчера процесса последовательной связи. С помощью простого интерфейса ввода-вывода УАПП может быть включен в компьютерную систему и обмениваться данными с процессором. Если путем программирования УАПП задать скорость передачи данных, тип контроля четности, размер символа, протоколы формирования и проверки кадра, то в дальнейшем управление процессом последовательной связи осуществляется автоматически. В данной главе рассматривается следующая фаза процедуры последовательной связи - обмен данными между УАПП и внешним миром. Глава начинается с обсуждения интерфейса RS-232/V.24, который de facto является коммуникационным стандартом для компьютерных систем. Описываются электрические и механические характеристики этого интерфейса, а также назначение и использование сигналов на его линиях. В главе анализируется также перенос идеальной модели интерфейса RS-232 в реальный мир на примере типичной реализации асинхронного коммуникационного (связного) адаптера для IBM PC. Далее следуют несколько примеров, иллюстрирующих некоторые ситуации, характерные для реальных интерфейсов, и рассмотрены кабельные соединения, необходимые для осуществления эффективной связи. В конце главы кратко изложены методы программирования для реализации процедуры последовательной связи, управляемой прерываниями, с помощью IBM PC. Отметим, что эта глава не заменяет изложения стандартов RS-232 или V.24. Не является она и полным руководством по устройству адаптера последовательного порта для IBM PC. Дополнительную информацию по этим вопросам можно получить из источников, приведенных в списке литературы в конце книги (приложение Д). 1 2 3 4 5 6 7 8 ... 38 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |