|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Системы передачи данных 1 2 3 4 5 6 7 ... 38 говом регистре приемника даже в том случае, когда данные принимаются с ошибками кадрирования и четности. Микросхема 8250 может обрабатывать символы длиной от 5 до 8 разрядов. При записи символа длиной менее 8 разрядов микросхема заносит ё1чэ в поле младших разрядов 8-разрядного БРП. Значения неиспользуемых разрядов не определены и перед использованием полученных данных должны маскироваться процессором. БРП адресуется как УАПП-регистр О, то есть так же, как РХП. Однако БРП определяется как регистр только для считывания. Хотя оба этих регистра имеют в УАПП один и тот же адрес, пространственно они разделены. Например, запись символа в РХП в тот момент, когда в БРП находится принятый нечитаемый символ, не влияет на последний. РХП используется также в комбинации с регистрами делителя скорости передачи (описываемыми ниже в данном разделе) для настройки микросхемы 8250 на определенную скорость передачи в бодах. Формат БРП показан на рис. 3.2. Первым с линии последовательной передачи приходит самый младший разряд данных. Микросхема 8250 работает в соответствии с принятым соглашением о порядке передачи разрядов и перестраивает принятые данные таким образом, чтобы самый младший разряд символа попал в позицию самого младшего разряда БРП. Регистр управления линией, РУЛ (LCR). Этот регистр разбит на семь полей. Значения разрядов, записываемые в данный регистр, определяют асинхронный формат данных, используемый при операциях приема и передачи. Вместе с регистрами делителя скорости передачи (описывг1емым далее в данной главе) РУЛ используется также для настройки микросхемы 8250 на определенную скорость передачи в бодах. РУЛ адресуется как УАПП-регистр 3 и доступен как для записи, так и для считывания. Формат РУЛ показан на рис. 3.3. Назначение каждого из полей регистра объясняется ниже. 1. Разряды 1-0: длина символа. Содержимое этого двухразрядного поля определяет число информационных разрядов, которые должны рассматриваться как один символ. Установленное число информационных разрядов передается или принимается как один асинхронный кадр. Длина символа может варьироваться в пределах 5-8 разрядов и задается путем установки значений двух разрядов в рассматриваемом поле по следующей схеме: Рис. 3.3. Регистр управления линией (РУЛ)

Разряд доступа к регистрам делителя скорости передачи 1 - Раэрмиение доступа г регистрам делителя Установка сигнала BREAK 1 - Послать сигнал BREAK Тип контроля четности 00 - Проверка на нечетнсжть 01 - Проаер на четность 10 - МАРК-контроль 11 - 8РАСЕ- онтроль Длина символа 00 = 5 разрядов 01 6 разрядов 10 = 7 разрядов 11=8 разрядов Число стоповых битов 0 - Гбит 1 = ? бит. если длина символа = 6. 7 или 8; 1.5 Бит. если длина символа = 5 разрядов Разрешение контроля четности 1 Включить бит четности Разряд 1 Разряд О Длина символа 0 0 5 разрядов 0 16 разрядов 10 7 разрядов 118 разрядов В карте данных микросхемы 8250 термины символ и слово не различаются, когда речь идет о группе информационных разрядов, передаваемых или принимаемых с помощью УАПП (такое использование этих терминов не имеет ничего общего с процессорными определениями 8-разрядных символов и 16-разрядных слов данных). Поэтому в некоторых справочных руководствах по УАПП разряды О и 1 (WLS0 и WLS1) РУЛ называются разрядами выбора длины слова. Каким бы ни был выбран размер символа, данные передаются с шины данных процессора в микросхему 8250 побайтно. Когда выбираются символы с числом разрядов, меньшим 8, эти разряды занимают поля младших разрядов передаваемых байтов; значения неиспользуемых разрядов игнорируются при передаче и остаются неопределенными при приеме. 2. Разряд 2: число стоповых битов (STB). Это поле используется для задания числа стоповых битов, добавляемых к каждому кадру при передаче. Установка этого разряда в О приводит к добавлению одного стопового бита к каждому передаваемому символу. Установка В 1 обеспечивает добавление двух стоповых битов к символам длиной 6, 7 или 8 разрядов. Если выбран 5-разрядный символ, установка рассматриваемого поля в 1 приводит к генерации 1,5 стоповых битов. Понятие половины стопового бита, возможно, покажется странным, но вспомним, что стоповый бит в действительности совсем не бит. Это просто период времени, в течение которого канал связи поддерживается в состоянии MARK. Поэтому передача 1,5 стоповых битов означает просто удержание канала в состоянии MARK в течение времени, составляющего 150% от времени действия одного элементарного сигнала. Отметим, что, принимая данные, микросхема 8250 проверяет только первый стоповый бит при любой установке данного поля. Эта операция описывается неправильно в некоторых технических справочниках. 3. Разряды 5-3: контроль четности. Содержимое этого поля определяет, будет ли бит четности генерироваться при передаче данных и проверяться при их приеме (если бит четности используется, он находится между последним разрядом данных и первым стоповым битом). По отдельности эти разряды определяются следующим образом: разряд 3 - разрешение контроля четности (PEN), разряд 4 - выбор четного/нечетного контроля (EPS), разряд 5 - выбор константного контроля (SPS). Установка значений этих разрядов определяет правила генерации и проверки бита четности в соответствии с табл. 3.1. Разряд разрешения контроля четности (PEN) включает или выключает процесс генерации и проверки бита четности. Если этот разряд установлен в О, то контроль четности не используется независимо от установки разрядов 4 и 5. Если PEN = 1, то тип используемого контроля четности выбирается путем задания определенных комбинаций установок рг1зрядов 4 и 5. Если PEN = 1 и SPS = О, выбирается проверка на нечетность или четность в зависимости от установки разряда выбора четного/нечетного контроля. При EPS = 1 (проверка на четность) значение бита четности выбирается таким образом, чтобы разряды символа и бит четности в совокупности содержали четное число логических единиц. Аналогично, при EPS = О (проверка на нечетность) значение бита четности выбирается таким образом, чтобы рг1зряды символа и бит четности в совокупности содержали нечетное число логических единиц. Например, при передаче символа 1011011b с использованием проверки на четность бит четности будет установлен в 1. Если разряд выбора константного контроля (разряд 5) установлен в 1, тип контроля четности, определяемый разрядом 4, изменяется. Теперь при установке разряда 4 в О выбирается MARK-контроль. Таблица 3.1. Выбор типа контроля четности Разряд 6 (SPS) Разрдц 4 Разряд 3 (EPS) (PEN) Тип контроля

Это означает, что бит четности всегда генерируется и проверяется как логическая 1 (MARK). Установка разряда 4 в 1 приводит к генерации и проверке бита четности как логического О (SPACE). Это SPACE-контроль. Поскольку величина константного бита четности никак не зависит от значений информационных разрядов символа, он не может указать на ошибку, кроме изменения значения самого бита четности. При проверке на MARK- или SPACE- 4eTHocTb величина бита четности просто всегда остается при выбранном значении. Поэтому мне кажется, что в этом случае можно было бы использовать более наглядный термин - липкая (sticky) чeтнocть Действительно, в Техническом справочнике по дополнительному оборудованию и адаптерам фирмы IBM (раздел Последовательный/параллельный адаптер ) о константной четности говорится как о приклеенной четности {stuck parity). Это один из примеров более наглядного, хотя и неофициального термина. Говоря о наглядности данного термина, автор, вероятно, имеет в виду ассоциативное представление константного бита четности к&к наклейки (липкого ярлыка) на символе с надписью MARK или ЗРАСБ . - Прим. перев. Существуют некоторые неочевидные применения константной четности. Предположим, например, что вам нужно обеспечить гарантированную передачу только символов АЗСП-кода (со значениями от О до 127) в систему, использующую 8-разрядные символы без контроля четности. Вы можете, конечно, накладывать на каждый байт маску 7Fh перед его передачей, однако имется более простой способ. Нужно просто запрограммировать п^)едглощий УАПП на использование 7-разрядных символов и SPACE-контроль. Самый старший разряд каждого байта будет при этом принудительно устанавливаться в 0. 4. Разряд 6: установка сигнала BREAK (ВС). Установка этого разряда непосредственно определяет выходной сигнал микросхемы 8250. Разряд используется для генерации сигнала BREAK. При его установке в 1 сигнал на последовательном выходе (SOUT) микросхемы принудительно устанавливается в состояние SPACE и остается в этом состоянии независимо от изменений всех других параметров передатчика. Такое состояние сохраняется до тех пор, пока в данный разряд не будет записан 0. Сигнал BREAK обычно используется для того, чтобы привлечь внимание связанного с передатчиком терминала или системы. 5. Разряд 7: разряд разрешения доступа к регистрам делителя скорости передачи (DLAB). Для обращения к БРП, РХП и РРП*) этот разряд необходимо установить в 0. При DLAB = 1 указанные регистры перестраиваются на обращение к регистрам делителя скорости передачи. Доступ к старшему и младшему байтам делителя скорости передачи осуществляется через регистры О и 1 УАПП соответственно. Операция установки делителя обсуждается ниже в данном разделе. Регистр состояния линии, РСЛ (LSR). Этот регистр разбит на шесть полей, указывающих текущие параметры процесса передачи данных. Процессор может проверять установки этих полей путем считывания их значений из РСЛ и поразрядного анализа. Заметим, что операция считывания информации из этого регистра приводит к автоматическому сбросу значений некоторых полей. Сохранение значений разрядов РСЛ - забота программиста. РСЛ адресуется как УАПП-регистр 5. Этот регистр обычно рассматривается как регистр только для считывания. Хотя для исходной микросхемы INS8250 операция записи не запрещена, тем не менее запись в РСЛ может вызвать проблемы при использовании микросхем-аналогов, выпускаемых другими фирмами. Например, Регистр разрешения прермвапкя (см. ниже). - Прим. перев. прежде чем принимать данные в последовательной форме, нужно сначала удалить предыдущий символ из буферного регистра приемника (БРП). Это следует делать путем считывания этого символа из БРП (с одновременной автоматической очисткой разряда готовности данных РСЛ), а не путем непосредственной записи О в этот разряд. Формат РСЛ показан на рис. 3.4. Разряд 7 этого регистра установлен в О, и его значение не изменяется. Назначение каждого из остальных полей РСЛ объясняется ниже. 1. Разряд 0: готовность данных (DR). Когда поступающий символ полностью принят микросхемой 8250 и передан в буферный регистр приемника, разряд готовности данных устанавливается в 1. Нет необходимости (хотя это допустимо) осуществлять очистку этого разряда вручную; считывание символа из БРП приводит к автоматическому сбросу DR в 0. 2. Разряд 1: ошибка переполнения (ОЕ). Логические схемы приемника в микросхеме 8250 работают непрерывно. Если символ получен, собран в сдвиговом регистре приемника и передан в БРП, а предыдушлй символ еще не считан процессором, то этот предыдущий символ безвозвратно теряется. Такая ситуация называется ошибкой переполнения приемника^\ и при ее обнаружении микросхема 8250 устанавливает разряд ошибки переполнения в 1. Этот разряд автоматически сбрасывается в О, когда процессор считывает информацию из РСЛ. Обратите внимание, что не имеется никакой информации относительно числа символов, перезаписываемых в БРП с момента последнего обращения процессора к РСЛ. 3. Разряд 2: ошибка четности (РЕ). Когда символ принят, значение бита четности перерассчитывается в соответствии с параметрами, установленными в РУЛ. Если полученное значение не совпадает со значением бита четности, принятого вместе с символом, разряд ошибки четности устанавливается в 1. Если обнаружена ошибка четности, то такая установка сохраняется даже в том случае, когда следующие символы принимаются с правильным значением четности. РЕ-разряд автоматически сбрасывается в О только при считывании процессором информации из РСЛ. Заметим, что в документации, предоставляемой с микросхемой 8250, а также и в другой технической документации подразумевается, что РЕ-разряд позволяет фиксировать ошибки четности только При проверке на четность и нечетность. Это неверно. Ошибки четности обнаруживаются и сообщаются процессору как при проверке на Или ошибкоИ из-за перезаписи приемника. - Прим. перев. §c Ш a. s -3 О -

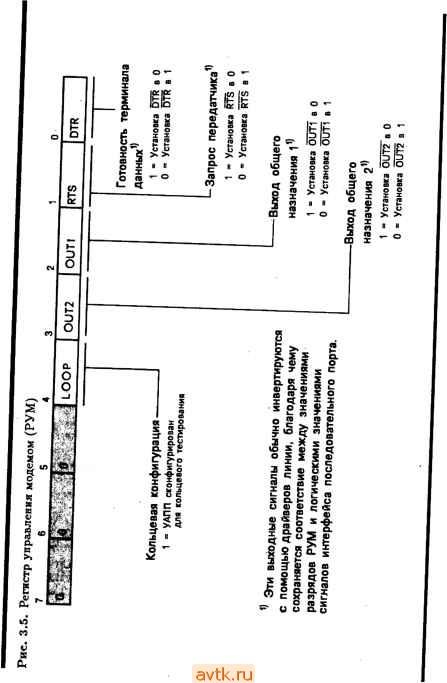

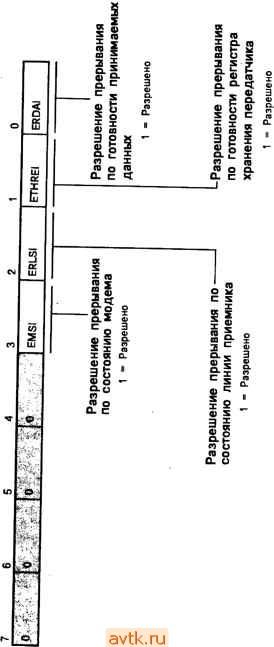

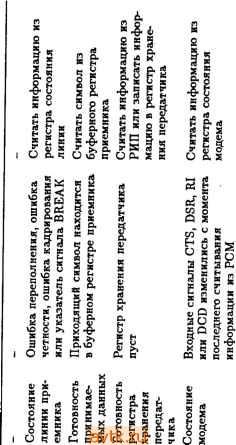

Oreo. X V n IS i- i I s a о - £8- с о четность и нечетность, так и при использовании MARK- и SPACE-контроля. 4. Разряд 3: ошибка кадрирования (FE). Кадр считается недействительным, если он не завершается по меньшей мере одним стоповым битом. Если бит, следующий за последним разрядом данных или битом четности, не есть стоповый бит (т. е. он не имеет значения MARK), микросхема 8250 сообщает об ошибке кадрирования и уста-навливг1ет разряд ошибки кадрирования РСЛ в 1. Принятый символ тем не менее передается в БРП. РЕ1-рг1зряд автоматически сбрасывается в О, когда процессор считывг1ет информацию из РСЛ. При обнаружении ошибки кадрирования микросхема 8250 пытается автоматически восстановить синхронизацию, используя предположение, что неправильный стоповый бит на самом деле является стартовым битом для следующего символа. Конструируется новый символ, начинающийся с этого нового стартового бита. 5. Разряд 4: прерывание по сигналу BREAK (BI). Микросхема 8250 устанавливает этот разряд в 1 всякий раз, когда на ее последовательном информационном входе (SIN) реализуются условия сигнала BREAK. Для реализации сигнала BREAK вход SIN должен удерживаться в состоянии SPACE в течение промежутка времени, превышающего длительность одного кадра (кадр включает в себя стартовый бит, информационные разряды, бит четности и стоповый бит). Для снятия сигнала BREAK вход SIN должен оставаться в состоянии MARK в течение промежутка времени, не меньшего половины длительности одного элементарного сигнала (бита). Заметим, что если сигнал BREAK имел место, то при его снятии установка В1-разряда сохраняется. В1-разряд сбрасывается в О, когда процессор считывает информацию из РСЛ. 6. Разряд 5: готовность регистра хранения передатчика (THRE). Этот разряд устанавливается в 1, когда микросхема 8250 передает символ из РХП в сдвиговый регистр передатчика. Тем самым сообщается, что РХП пуст и готов к приему следующего символа для передачи (см. выше обсуждение РХП). Запись нового символа в РХП в тот момент, когда ТН11Е-рг1зряд имеет нулевое значение, приводит к перезаписи непереданного символа, находящегося в РХП, и его безвозвратной потере. Такая ситуация называется ошибкой переполнения передат\ика^\ но эта ошибка не обнаруживается микросхемой 8250 и, естественно, о ней не выдается никаких сообщений. THRE3-pa3pHfl сбрасывается в О, когда процессор записывает сим- Или отгибкой л-зо перезаписи передатчика. - Прим. перев. вол в РХП. Запись в этот разряд не приводит к изменению его значения. Обратите внимание, что установка этого разряда отражает только состояние РХП. Тот факт, что РХП пуст, не означает, что пуст сдвиговый регистр передатчика или что прекратилась последовательная передача данных (см. следующее ниже описание TSRE-разряда). 7. Разряд 6: готовность сдвигового регистра передатчика (TSRE). Когда символ, находившийся в сдвиговом регистре передатчика, уже передан, а новый символ еще не готов для передачи из РХП, микросхема 8250 устанавливает этот разряд в 1. В дальнейшем, когда микросхема передает символ из РХП в сдвиговый регистр передатчика, TSRE-разряд сбрасывается в 0. Запись в этот разряд не приводит к изменению его значения. В некоторых документах этот разряд называют разрядом готовности передатчика (ТЕМТ), подчеркивая тем самым, что необходимым условием установки этого разряда в 1 является готовность как РХП, так и сдвигового регистра передатчика. Последовательную переда-, чу нельзя считать завершенной, пока оба разряда THRE и TSRE не будут установлены в 1. Регистр управления модемом, РУМ (MCR). Этот регистр обеспечивает контроль выходных сигналов, посылаемых от микросхемы 8250 к модему (устройству сопряжения) или к устройству, эмулирующему модем. РУМ - регистр для записи и считывания, адресуемый как УАПП-реглстр 4. Он разбит на пять полей. Формат РУМ показан на рис. 3.5. Разряды 7, б и 5 этого регистра установлены в О, и их значения не изменяются. Назначение камедого из остальных полей регистра объясняется ниже. Следует отметить, что сигналы управления модемом, генерируемые микросхемой 8250, комплементарны к соответствующим запротоколированным сигналам интерфейса EIA RS-232, т. е. их физическое значение противоположно их логическому смыслу. Этот факт отмечается в тексте с помощью черты над обозначением сигнала. Эти комплементарные сигналы от УАПП обычно подаются на внешние устройства через канальные инверторы-формирователи. Инверсия обеспечивает полное соответствие между значениями разрядов регистра и логическими значениями соответствующих выходных сигна- лов. Эта ситуация подробно обсуждается в гл. 4, где также объясни- ется использование рассматриваемых управляющих сигналов. 1. Разряд 0: готовность терминала (DTR). Сигнал готовности терминала посылается от микросхемы 8250 к связанному с ней  устройству. Установка этого поля непосредственно определяет знэг чение сигнала на выходе DTR микросхемы. При DTR = 1 на выходе DTR устанавливается 0. Аналогично, запись О в это поле приводит к установке 1 на выходе DTR. 2. Разряд 1: запрос передатчика (RTS). Этот сигнал посылается от микросхемы 8250 к связанному с ней устройству. Запись О в это поле приводит к установке 1 на выходе RTS. При RTS = 1 на выходе RTS устанавливается 0. 3. Разряд 2: выход общего назначения 1 (0UT1). Разряд 0UT1 контролирует сигнал на выходе общего назначения OUT1 микросхемы 8250. Использование этого выхода зависит от аппаратной реализации. Запись О в рассматриваемое поле приводит к установке 1 на выходе 0UT1. Аналогично, установка этого поля в 1 приводит к установке О на выходе 0UT1. 4. Разряд 3: выход общего назначения 2 (0UT2). Разряд OUT2 контролирует сигнал на выходе общего назначения OUT2 микросхемы 8250. Использование этого выхода зависит от аппаратной реали-зации. Сброс поля OUT2 в О приводит к установке 1 на выходе 0UT2. Аналогично, установка этого поля в 1 приводит к установке О на выходе 0UT2. При использовании в асинхронном коммуникационном адаптере (ШМ-РС) необходимо надлежащее программирование этого поля для обеспечения ввода-вывода по прерываниям. Детали этой реализации обсуждаются в гл. 4. 5. Разряд 4: петлевая конфигурация (LOOP). Этот разряд используется для установки локальной петлевой конфигурации микросхемы 8250, обеспечивающей выполнение одного из встроенных самотестов. При установке этого разряда в 1 в работе микросхемы 8250 происходят следующие изменения. Последовательный вход (SIN) микросхемы отсоединяется от его нормального внешнего соединения и подключается внутренним образом к последовательному выходу (SOUT) микросхемы. Выход сдвигового регистра передатчика присоединяется к входу сдвигового регистра приемника. Четыре старших разряда регистра состоячния модема (см. ниже) отключаются от своих внешних соединений и связываются внутренним образом с четырьмя младшими разрядами РУМ по следующей схеме. DCD (разряд 7) RI (разряд 6) DSR (разряд 5) OUT2 (разряд 3) 0UT1 (разряд 2) DTR (разряд 0) RTS (разряд 1) CTS (разряд 4) Когда такая реконфигурация системы завершена, любые данные, которые направляются к микросхеме 8250 для передачи, сразу же принимаются. Сравнивая посланные данные с принятыми, процессор может удостовериться, что тракты передачи и приема данных в микросхеме 8250 функционируют нормально. Система прерываний приемника и передатчика также остается полностью работоспособной. Тестирование системы прерываний можно осуществить путем записи 1 в любой из четырех младших разрядов регистра разрешения прерывания и проверки выполнения соответствующего прерывания. Система прерываний микросхемы 8250 обсуждается ниже в этой главе, а также в гл. 4. Регистр состояния модема, РСМ (MSR). Этот регистр разбит на семь полей, которые указывают не только текущие значения си1 налов состояния модема, но и фиксируют изменения этих сигналов с момента последнего считывания информации из РСМ. Кроме того, при петлевом тестировании микросхемы разряды 4-7 этого регистра соединяются с разрядами 0-3 регистра управления модемом, как было указано в предыдущем разделе при описании РУМ. Процессор может проверять установки этих полей путем считывания их значений из РСМ и поразрядного анализа. Заметим, однако, что при считывании информации из этого регистра все его разряды автоматически сбрасываются в 0. Сохранение значений разрядов РСМ при этой операции - забота программиста. РСМ адресуется как УАПП-регистр 6. Это регистр как для записи, так и для считывания. Формат этого регистра, известного также как регистр состояния устройства сопряжения, показан на рис. 3.6. Назначение каждого из полей РСМ объясняется ниже. 1. Разряд 0: изменение сигнала Сброс передатчика (DCTS). Любое изменение уровня сигнала на входе CTS микросхемы 8250 (от О к 1 или от 1 к 0) приводит к установке этого рг1зряда в 1. 2. Разряд 1: изменение сигнала Готовность модема (DDSR). Любое изменение уровня сигнала на входе DSR микросхемы 8250 приводит к установке этого рг1зряда в 1. Регистр состояния модема Регистр управления модемом 3. Разряд 2: задний фронт сигнала Указатель вызовов (ТЕШ). Изменение сигнала на входе RI микросхемы 8250 от низкого уровня к высокому приводит к установке этого разряда в 1. С учетом компле-ментарности сигналов на выходах микросхемы и сигналов на линии это соответствует изменению сигнала RI от высокого уровня к низкому: другими словами, переходу к заднему фронту сигнала указателя вызовов. 4. Разряд 3: изменение сигнала Указатель несущей (DDCD). Любое изменение уровня сигнала на входе DCD микросхемы 8250 приводит к установке этого разряда в 1. В некоторых документах вместо термина указатель несущей используется эквивалентный термин указатель сигнала на линии приема (с заменой обозначения разряда: DDCD на DRLSD). 5. Разряд 4: сброс передатчика (CTS). Значение этого разряда указывает в комплементарном виде текущее значение сигнала навхо-де CTS. При петлевом тестировании этот разряд соединяется с RTS-выходом РУМ. 6. Разряд 5: готовность модема (DSR). Значение этого разряда указывает в комплементарном виде текущее значение сигнала на вхо-де DSR. При петлевом тестировании этот разрад соединяется с DTR-выходом РУМ. 7. Разряд 6: указатель вызовов (RI). Значение этого разряда указывает в комплементарном виде текущее значение сигнала на входе RI. При петлевом тестировании этот разрад соединяется с 0UT1-выходом РУМ. 8. Разряд 7: указатель несущей (DCD). Значение этого разряда указывает в комплементарном виде текущее значение сигнала на входе DCD. В некоторых документах вместо термина указатель несущей используется эквивалентный термин указатель принимаемого сигнала (с заменой обозначения разряда DCD на RLSD). При петлевом тестировании этот разряд соединяется с ОиТ2-выходом РУМ. Регистр разрешения прерывания, РРП (IER). Этот регистр разрешает или запрещает по отдельности четыре типа прерываний, которые может генерировать микросхема 8250. Факт возникновения ситуации, связанной с разрешенным прерыванием, сообщается в регистр идентификации прерывания (РИП). Каждое отдельное прерывание может активизировать выход INTR микросхемы 8250. Запись 1 в разряды О, 1, 2 или 3 регистра разрешения прерывания - in X °-if s I с - 01 о о о s ° S 5 CO ш - £ S 5 r S f es - ° Ф a a i D D 8lSE g is CO > > 2 .J: о - ) о in Саш Q> О о II О > > разрешает генерацию соответствующего прерывания. Если возникает одно из условий, необходимых для генерации прерывания, когда соответствующий разряд разрешения прерывания установлен в 1, УАПП немедленно выдает команду на выполнение этого прерывания. Аналогично, сброс любого из четырех младших разрядов РРП в О приводит к блокировке соответствующего прерывания и удалению любого сигнала на прерывание из РИП. Запрещенное прерывание не сообщается в РИП и не активизирует INTR-сигнал. Однако все другие функции микросхемы 8250, включая обновление РСЛ и РСМ, выполняются обычным образом. Заметим, что в большинстве применяемых реализаций последовательного порта IBM PC прерывания, генерируемые УАПП, могут быть использованы только после некоторых дополнительных операций. Этот вопрос обсуиедается в гл. 4. РРП адресуется как УАПП-регистр 1 и является регистром для записи и считывания информации. Формат РРП показан на рис. 3.7. Разряды 4-7 этого регистра установлены в О, и их значения не изменяются. Назначение каждого из остальных полей РРП объясняется ниже. 1. Разряд 0: разрешение прерывания по готовности принимаемых данных (ERDAI). При ERDAI = О указанное прерывание запрещено. Установка этого разряда в 1 разрешает данное прерывание, и команда на прерывание выдается каждый раз, когда принятый символ передается из сдвигающего регистра приемника в БРП. 2. Разряд I: разрешение прерывания по готовности регистра хранения передатчика (ETHREI). Установка этого разрада в 1 разрешает указанное прерывание, и команда на прерывание выдается каждый раз, когда символ передается из РХП в сдвигающий регистр передатчика. Сброс этого поля в О блокирует данное прерывание. 3. Разряд 2: разрешение прерывания по состоянию линии приемника (ERLSI). Установка этого разряда в 1 разрешает указанное прерывание, и команда на прерывание выдается каждый раз, когда один из разрядов ОЕ, РЕ, ЕЕ или BI (разряды 1-4 регистра состояния линии) или сразу несколько этих разрядов устанавливаются в 1. Содержимое РСЛ может быть проанализировано для определения причины прерывания. Заметим, что данный разряд является общим переключателем для четырех возможных типов прерываний. Они не могут быть разрешены или запрещены по отдельности. 4. Разряд 3: разрешение прерывания по состоянию модема (EMSI). Установка этого разряда в 1 разрешает указанное прерывал ние. Это поле называют также разрядом разрешения прерывания по £  состоянию устройства сопряжения (EDSSI). Если указанное прерывание разрешено, то команда на его выполнение выдается каждый раз, когда один из разрядов DCTS, DDSR, ТЕШ или DDCD (разряды 0-3 регистра состояния модема) или сразу несколько этих разрядов устанавливаются в 1. Заметим, что этот разряд РРП является общим переключателем для четырех возможных типов прерываний. Эти прерывания не могут быть разрешены или запрещены по отдельности. Содержимое РСМ должно быть проанализировано для определения причины прерывания. Регистр идентификаи.ии прерывания, РИП (IIR). Для четырех типов прерываний, определяемых РРП, микросхема 8250 устанавливает приоритеты. Если возникают обстоятельства, приводящие более чем к одному типу прерываний, в регистр идентификации прерывания (РИП) сообщается только о прерывании с наиболее высоким приоритетом. Путем генерации прерывания только с наивысшим приоритетом микросхема 8250 помогает процессору с наименьшей затратой сил отслеживать процесс передачи данных. Четыре рассматриваемых типа прерываний записаны ниже в порядке убывания их приоритетов. Состояние линии приемника (наивысший приоритет) Готовность принимаемых данных Готовность регистра хранения передатчика Состояние модема (самый низкий приоритет) При возникновении прерывания процессор может считать информацию из РИП для определения причины прерывания. Пока идет процесс считывания, все действия, связанные с прерываниями, выполняются обычным образом и запоминаются микросхемой 8250, но содержимое РИП не обновляется. Как только информация из РИП считана, содержимое этого регистра модифицируется и отображает новое текущее состояние микросхемы. Завершив обслуживание текущего инициированного прерывания, процессор может идентифицировать и обрабатывать прерывание следующего более низкого приоритета в новом миницикле опроса РИП. РИП адресуется как УАПП-регистр 2. Этот регистр доступен только для считывания информации. Формат РИП показан на рис. 3.8. Разряды 3-7 этого регистра установлены в О, и их значения не изменяются. Назначение каждого из остальных трех полей объясняется ниже. п м Г<А, (В 3 о. Е Я- о 0) о. II = о о. с р m m о с II II н 85S := п m 2 о. Ф о. 1. Разрад 0: отложенные прерывания (ШР). Если нет отложенных прерываний, в этом поле будет находиться 1. Любое обстоятельство, генерирующее прерывание, приводит к сбросу этого поля в 0. Заметим, что используемая здесь терминология описывает прерывания с точки зрения УАПП, а не процессора. Поэтому отложенное прерывание есть просто указание того факта, что микросхема 8250 должна сообщить некоторую информацию о состоянии процесса последовательной передачи данных. Могут быть отложены несколько прерываний, но только прерывание с наивысшим приоритетом передается в поле идентификации прерывания. 2. Разряды 1-2: поле идентификации прерывания. Если в поле отложенных прерываний (разряд 0) находится логический О, то содержимое поля идентификации прерываний указывает прерывание с наивысшим приоритетом. Возможные прерывания, их приоритеты, типы, причины и действия, необходимые для их сброса, указаны в табл. 3.2. Регистры делителя скорости передачи. Микросхема 8250 содержит программируемый контроллер-генератор скорости передачи, обеспечивающий деление частоты внешнего опорного сигнала на коэффициент, который может изменяться от 1 до 65535. Результат деления представляет собой 16-фазную последовательность синхронизирующих импульсов, управляющих работой внутренних логических схем передатчика. Формула для определения делителя, обеспечивающего генерацию заданной скорости передачи в бодах, имеет вид: Делитель = ----, 16 X скорость передачи где / - частота внешнего опорного сигнала в герцах.Чаще всего для генерации внешнего опорного тактового сигнала используется кристалл-резонатор на частоту 1,8432 МГц. Фирма IBM выпуска^ ет высокоскоростные контроллеры последовательного порта, которые используют опорный сигнал с частотой 11,0592 МГц и способны передавать данные со скоростями до 345 600 бод. Таблица 3.3 представляет список делителей, обеспечивающих реализацию общепринятой сетки скоростей передачи при использовании кристалла-резонатора на частоту 1,8432 МГц. Делители для других скоростей передачи и других опорных частот легко рассчитываются по вышеприведенной формуле. Заметим, что некоторые ранние варианты микросхемы 8250 работают ненадежно при высоких скоростях передачи. Фирма National не рекомендует использовать нулевой делитель в любом случае. о n S e. g. с & 4. в с H в I  4< 1 2 3 4 5 6 7 ... 38 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |