|

|

|

Разделы

Публикации

Популярные

Новые

|

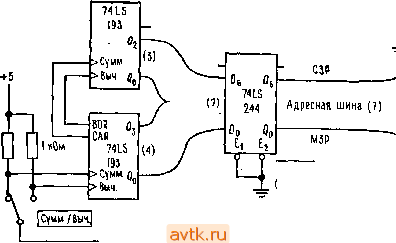

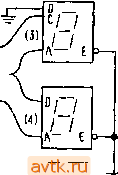

Главная » Сопряжение цифровых, аналоговых сигналов 1 ... 53 54 55 56 57 58 59 ки битов являются распространенной ошибкой. Можно пометить биты в соответствии с цветовым кодом для сопротивлений, т. е. обозначить нулевой бит черным цветом и т. д. 2) ИМС устанавливайте как можно ближе друг к другу. Если вы будете экономны, все должно уместиться на трех стандартных монтажных платах макетной панели, две из которых понадобятся для самого компьютера и еще одна - для различных периферийных устройств. 3) Обращение с ИМС МОП. Статические заряды на входных выводах могут разрушить схемы МОП, Любую ИМС МОП всегда устанавливайте после того, как иа макетной панели подключены все идущие от нее провода. Никогда ие касайтесь выводов пальцами; берите корпус только за торцы и всегда храните ИМС в проводящем пенопласте. Эта мера предосторожности относится (в наших лабораторных работах) только к ИМС ЦП и ЗУПВ. 19.!. Адресный счетчик и дисплей. При иключении, показанном на рис. 19.2, буфера с тремя состояниями остаются в резерве (ие используются) и выход счетчика всегда 1кОи  ENABLE счетчик адреса)  Защищенный от afedeirs и кнопочный выключатель ENABLE Рис. 19.2. Адресный счетчик и дисплей. Обратите вннманне, что не все выводы реверсивных счетчиков 74LS193 задействованы; как вам следовало бы поступить с неиспользованными входами? Справьтесь в приложении В. подаетси на шину адресов, так что дисплей показывает состояние счетчика. Проверьте при помощи кнопочного выключателя, что счетчик действительно может считать а обоих направлениях (т. е. суммировать и вычитать) и что при изменении направления не появляются паразитные счетные импульсы (возникновение такой проблемы могло бы означать, что поступающие от кнопки импульсы имеют не ту полярность). Подайте на вход ENABLE (разрешение) буфера сигнал высокого уровня. Объясните, что видите на дисплее. Теперь, отпирая и запирая буферы с тремя состояниями, исследуйте логическим пробником отдельные линии шины. Логический пробник устроен так, чтобы показывать неподключенное состояние при помощи свечения вполсилы. Вход ENABLE пока оставьте заземленным; этим входом, как и входом ENABLE дисплея (также заземленным), будет в случае необходимости управлять наш компьютер. 19.2. Шина данных и дисплеи. Соберите блок шины данных, как показано на рис. 19.3. Расположите разряды (СЗР), D,. . ., (МЗР) в порядке слева направо, поскольку при таком расположении (макетная панель смотрит на вас) набор битов представляет двоичное число; оба дисплея расположите аналогичным образом. Убедитесь, что при сигнале низкого уровня на линии WRITE (запись) дисплей показывает набор битов, который установлен на переключателе DIP, после чего проверьте ваше искусство в проведении преобразований из шестнадцатеричной системы счислении в двоичную. Переключатель шнц - DIP 1 ком D7 07 7US Do Uo El h СЗР Шина данных (в)  МЗР 3апись| ~) ENABLE : (дисплеи данных) Рис. 19.3. Шина данных и дисплей. На этой же схеме показано расположение выводов мини-01Р-переключателя. Адресная шина 17}  Шина данных t8) Выбор чипа

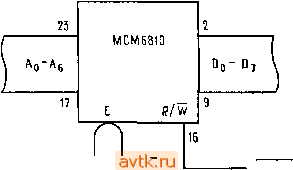

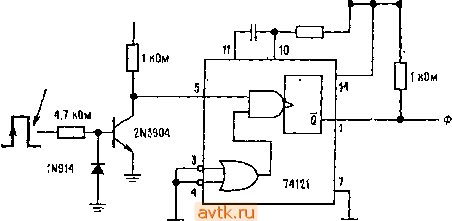

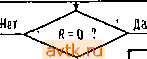

0 12 3 4 5 Рис. 19.4, Соединения выводов ИМС памяти. Корпус имеет 24 вывода; U - вывод 24, земля - вывод 1. 19.3. Память, ИМС памяти МСМ6810 имеет 128 ячеек по 8 бит и выполнена иа п-МОП-структурах. Она использует одни источник питания +5 В и имеет ТТЛ совместимые вход и выход, что для наших целей весьма удобно. Можете ли вы понять, с какой целью здесь и пользована необычная комбинация выводов выбора ИМС? Что надо делать с каждым из них, чтобы пользоваться па- мятью? Соедините вывод READ / WRITE (чтение / запись) с выключателем WRITE (запись), при помоши которого мы ранее в этой работе (часть 2) разрешали ввод данных на шину. Когда на линии WRITE имеется сигнал низкого уровня, данные через шину записываются в память. Если сдвинуть адресный счетчик на один шаг, те же данные будут записаны в следующую ячейку. Когда же на линии WRITE имеется сигнал высокого уровня, память сама выдает данные на шину данных, что позволяет вам узнавать содержимое каждой ячейки. Тщательно проверьте действие памяти при чтении и при записи, используя в качестве данных различные наборы битов; вы должны убедиться, что ни один бит не остается всегда в одном и том же состоянии. Проделайте это для нескольких ячеек во всем диапазоне адресов. 19.4. Прелще, чем вы уйдете. Не разбирайте плод ваших тяжких усилий! Самое интересное еще не начиналось! Напишите на макетной панели ваше имя и поместите ее в безопасное место, чтобы сохранить до следующего занятия. Лабораторная работа 20. Микропроцессор II Материал для чтения: гл. 10, разд. 10.12 и до конца сгр. 137-159, т. 2; введите в эту работу и приложение о процессоре Z 80. Задачи в основном тексте; дополнительные упражнения 7-9. Итак, час настал. Сейчас мы соединим микропроцессор Z 80 с блоками шин, которые были собраны в предыдущей работе. До того как можно будет запустить компьютер, нам придется позаботиться о некоторых дополнительных деталях, а именно о строби-ровании для управления доступом к шине и фиксируюишми схемами дисплеев (напомним, что все относяншеся сюда входы ENABLE пока заземлены) и об обеспечении системы тактовыми импульсами с нужными свойствами. Эти детали займут, вероятно, большую часть работы, к которой мы теперь приступаем. Прежде всего давайте познакомимся с микропроцессором Z 80. Расположение его выводов показано на рис. 1; 24 вывода из общего их числа 40 отведено под адресную шину (16 бит) и шину данных (8 бит), а остающиеся 16 выводов распределены между линиями питания и управляющими линиями. Большую часть этих линий мы будем в свое время использовать (или хотя бы обсуждать их работу), так что имеет смысл уже сейчас описать их назначение: BUSRQ (bus request - запрос шины ). Входная линия возбуждается сигналом низкого уровня. Когда этот вход активирован, компьютер в течение нескольких тактов-освобождает обе шины, которые после этого остаются неподключенными. Отключаются также и некоторые линии управления. К этому входу мы присоединим выключатель, который позволит нам отсоединять процессор от шины, что нужно для осуществления прямого доступа к памяти. BUSAK (bus asknowledge - подтверждение шины ). Входная линия, в активном состоянии низкий уровень. BUSRQ действует не мгновенно; прежде чем освободить шину, компьютер должен закончить выполнение команды, которую он начал выполнять до активизации входа BUSRQ, иначе впоследствии было бы невозможно правильно продолжить работу. Поэтому, чтобы избежать конкуренции на шине и связанных с ней неприятностей, для разрешения внешнего доступа к шинам приходится использовать специальный выход BUSAK. Мы соединим его с разрешающим входом ENAB-LE буфера адресногасчетчика, чем и достигаем указанной цели. Кроме того, мы подключим к нему светодиодный индикатор, который будет показывать, производится ли ручной доступ к шинам. RESET ( сброс ). Входная линия активизируется сигналом низкого уровня. Этот вход инициирует компьютер, при этом все флаги состояния сбрасываются и начинается исполнение команд с ячейки 0000. HALT ( останов ). Выходная линия, в активном состоянии низкий уровень. После выполнения команды HALT па этом выходе устанавливается низкий уровень; в состояние с высоким уровнем он может вернуться только под действием RESET или соответствующего прерывания. К этому выходу мы также подключим светодиод, который будет показывать, работает ли компьютер. MREQ (memory request - запрос памяти ). Выход с тремя состояниями, в активном состоянии низкий уровень. Синхронизирующий сигнал MREQ указывает, что в данный момент происходит выполнение операций, требующих обращения к памяти. МГ (memory cycle 1 - цикл памяти ). Выход с тремя состояниями, в активном состоянии низкий уровень. Ml - синхронизирующий сигнал. IORQ (Input / output request - запрос ввода / вывода ). Выход с тремя состояниями, в активном состоянии низкий уровень. Синхросигнал IORQ показывает, что в данный момент происходит выполнение команды IN или OUT. Он используется для подключения периферийных устройств к шине данных. RD (read чтение ). Выход с тремя состояниями, активное состояние с низким уровнем. Строб для считывания данных из памяти или В/В. WR (write - запись ). Выход с тремя состоиииями, активное состояние с низким уровнем. Строб для записи в память или В/В. Чтобы лучше понять назначение последних пяти выходных линий синхронизации управления (э также выхода RFSH dynamic memory refresh - регенерация динамической памяти , которым мы ие пользуемся), надо рассмотреть соответствующие временные диаграммы в приложении, посвященном микропроцессору Z 80. Кроме того, позже сегодня мы еще будем исследовать эти выходы при помощи осциллографа. Наконец, есть еще три входа, которые мы вообще не будем использовать; каждый из них мы заблокировали, приложив к иему-f 5 В: WAIT ( ожидание ); вводит ждущие машинные такты, чтобы продлить циклы доступа к памяти и тем самым обеспечить возможность работы с медленно действующей памятью. INT (interrupt request - запрос прерывания ). NMI (поп maskable interrupt request- не маскируемый запрос прерывания ); осушествляет переход к ячейке 0066ie. Аналогичен входу TRAP микропроцесса 8085. 20.1, Центральный процессе. Подключите ваш Z 80, как показано на рис. 20,1. Обратите внимание на то, что входы микропроцессора мы никогда не оставляем свобод- + 5 - / Шина У / данных(8) v .5-1 MREQ An А, Ф Ь Ь ь 2 80 н h As A* HMT MRtQ 1Щ RESH M, RESET WAIT WR RD Адресная шинз 1П КОМ 10 ком BU5RQ [\~\ [сброс! RD BUSAK виьак рис. 20.1. Организация центрального процессора. Линии RUN и BUSAK соединены со светодиодными индикаторами на макетной панели. ными, поскольку должны исключить возможность случайных операций; в то же время неиспользованные входы, как, например, старшие адресные линии, оставлены неподключенными. Выводы для битов данных расположены в на}бычном порядке, так что не забудьте еще раз проверить, правильно ли они соединены с уже смонтированной шиной данных. Символ £f использован для обозначения главного тактового генератора, который мы смонтируем в части 4 этой работ1Ы^ Теперь соедините выход BUSAK с двумя входами ENABLE буфера с тремя состояниями, через который наш реверсивный счетчик передзет адрес иа адресную шилу. Тем самым счетчику автоматически будет позволено адресовать память, когда компьютер будет освобождать шину в ответ на замыкание выключателя BUSRQ. 20.2. Разрешение дисплея адреса. Вам, вероятно, не вполне ясно, почему адресный дисплей нельзя просто оставить постоянно включенным. Позже, когда мы будем исследовать адресную шину при помош,и осциллографа, ответ на этот вопрос станет более очевидным. При нормальной работе микропроцессор Z 80 высылает на шину помимо адресной информации еще и адреса регенерации , которые нужны только для работы 9 RD Е(адресный дисплей) Рис. 20.2. Схема разрешения адресного дисплея. Для двух вентилей используйте счетверенный вентиль НЕ-ИЛИ 74LS02; Ф обозначает главный тактовый сигнал ЦП (вывод 6 микропроцессора Z 80); RD - это выход Z 80 (вывод 21); BUSAK получается из BUSAK при помощи инвертора (часть 20 1) с динамической памятью (см. разд. П. 10), причем посылка обоих типов адресов чередуется. Нас же интересуют лишь адреса первого типа, и во избежание путаницы адреса регенерации нельзя допускать иа дисплей. Если посмотреть на временные диаграммы в приложении с описанием микропроцессора Z 80, то можно заметить, что для этой цели как раз подходит импульс RD; логическое И с синхроимпульсом оказывается нужным из-за необычно большого времени захвата (50 не) фиксирующих входов дисплеев фирмы Hewlett - Packard, а логическое ИЛИ с импульсом BUSAK включает дисплей при осуществлении ручного управления шиной. Когда будете соединять выход этих вентилей с разрешающими входами (ENABLE) дисплея, не забудьте отключить их от земли (с которой они были перед тем соединены). 20.3. Разрешен не работы памяти. Поскольку Z 80 с его ограниченным числом выводов не имеет специального сигнала считывание из памяти , мы вынуждены использовать вместо него RD AND MREQ, который формируется при помощи соответствующих MREQ RD -<i >-ЕМШ ВиЗАК Рис. 20.3. Ъкема разрешения работы памяти. MREQ, RD и BUSAK - это сигналы, получаемые от процессора (часть 1). Для построения этой схемы воспользуйтесь второй половиной схемы 74LS02, которую мы применили в части 3. вентилей. Чтобы это понять, надо посмотреть временные диаграммы в приложении: MREQ истинно для операций как считывание из памяти , так и регенерации*, которую мы должны исключить; RD истинно во время операций ввода / вывода; оба они истинны только в течение считывания из памяти . Логическое ИЛИ с импульсом BUSAK использовано здесь с той же целью, что и выше в разд. 2. Какая логическая схема понадобилась бы, чтобы позволить ЦП осуществлять также и запись в память? Здесь уместно вспомнить, что уровень R/W naMHTH ие может все время оставаться постоянно высоким и что надо также предусмотреть ручную запись в память. Микропроцессор Z 80 имеет выход WR, который в точности аналогичен выходу RD. На самом деле такое усовершенствование не является обязательным; Z 80 имеет достаточно регистров для всех необходимых вычислений, так что запись в память никогда нам не понадобится. Конечно, если вы попытаетесь написать для этого компьютера программы, требующие записи в память, вам придется наделить его (см приложение) такой способностью, однако имейте в виду, что обладание ею может оказаться поистине опасным, если ваша программа по ошибке начнет переписывать саму себя1 Теперь отсоедините от земли и соедините с ЕМЕМ один из входов CS i> ИМС памяти. 20.4. Тактовый генератор. Эта схема имеет три функции: 1) Формирование отрицательных импульсов малой длительности для всех входных частот. Такой способ синхронизации рекомендован для микропроцессора Z 80. 2) Приведение их параметров в соответствие со стандартами ТТЛ (микросхема 74I2I имеет на входе внутренний триггер Шмитта). +5 +5 100 пФ АЛ кОм Генератор сигнала  т НС Рис. 20.4. Схема тактового генератора. 3) Защита микропроцессора Z 80от перегрузки на его тактовом входе, которая была бы возможной при непосредственном подключении генератора сигналов. Подайте на вход схемы сигнал от генератора сигналов и посмотрите при помоши осциллографа, что происходит на ее выходе. При высокой входной частоте иа выходе можно наблюдать импульсы длительностью 200 не. После того как получены тактовые импульсы с нужными свойствами, следует проверить, как выполняется последовательность запроса н подтверждения шины; после того, как мы вышлем запрос шины (низкий уровень на BUSRQ, т. е. выключатель замкнут), в течение нескольких тактов должен загореться индикатор BUSAK, а после снятия запроса этот индикатор должен погаснуть. Пока эта последовательность не начнет правильно действовать, продвигаться дальше нельзя. Если она не работает, проверьте логическим пробником тактовый генератор и убедитесь, что входы ENABLE, которые управляются выходом BUSAK. не остались заземленными. Теперь, когда BUSAK получен, проверьте, что при помощи адресного счетчика и DIP переключателя вы действительно можете осуществить считывание нз памяти и запись в иее, после чего введите следующую программу: Адрес 00 01 02 Данные Метка 00 Begin: СЗ 00 00 Операции Комментарии NOP ; нет операции = ничего не делать NOP ; то же самое JMP Begin ; перейти обратно к первой команде Программа 20.1. Повторяйте цикл Все программы в этой книге будут использовать этот формат, который типичен для выходных распечаток ассемблера. Специально отметим, что трехбайтовая команда JMP занимает только одну строку и что столбец данные имеет три входа. Помните это, когда будете вводить программу, и не записывайте их все три в одну ячейку памяти. Chip select - выбор чипа.- Прим. перее. 20.5. Простая программа. Программа 20.1 вводит наш компьютер в бесконечно повторяющийся никл, поэтому мы можем следить на осциллографе за тем, как он действует. Введите эту программу в первые пять ячеек ЗУПВ. Выполнение ее начните при помощи следующей последовательности действий: I) восстановите связь ЦП с шиной, для чего подайте на линию BUSRQ сигнал высокого уровня, затем 2) на мгновение переведите вход RESET в состояние с низким уровнем; это должно заставить ЦП извлечь первую команду из ячейки OOOOie. При тактовой частоте в несколько герц наблюдайте, как ЦП последовательно извлекает команды. Зачем вообще он должен просматривать ячейки 03 и 04? Теперь + 5 1 22 иОм , Подключение осциллографа 15 ком Рис. 20.5. На осциллограф поступает ~2,0 В, когда шина ие подключена. С другой стороны, такое соединение не слишком сильно нагружает шину. возьммте более высокую тактовую частоту и перейдите к наблюдениям с осциллографом. Чему равна максимальная частота, при которой компьютер еще может правильно действовать? Вероятно, вы сочтете полезным посмотреть на выход Ml (вывод 27), сигнал на котором имеет низкий уровень в течение двух первых тактов каждой команды ( извлечение КОПа ), Две команды NOP и одну JMP в нашей последовательности можно при этом опознать по их различным длинам. Запуская осциллограф внешним импульсом Ml и получая на его экране неподвижную кривую, мы можем сравнивать тактовый сигнал в одном из каналов с различными управляющими уровними в другом. Исследуйте те из них, которые нужны для заполнения временной диаграммы на рис. 20.6. Чтобы увидеть неподключенное состояние шины (это нужно для двух члл/шлАЛУштл/тлллА MREQ RD Рис. 20.6. Временная диаграмма. Нанесите недостающие лиини. Правильные соотношения фаз должны быть выдержаны, позаботь *есь об этом. последних строк диаграммы), вам придется использовать трюк, который показан на рис. 20.5. На диаграмме изобразите неподключенное состояние как уровень, расположенный посередине между Н и L. 19 Ml 62 Сравните ваш ответ с временными диаграммами в приложении Б (описание Z 80) и проверьте, согласуются ли ваши оценки длин команд с теми длинами, которые обозначены в приложении. Кривая для бита О адресной шины должна поначалу вас смутить. Период повторения оказывается в этом случае вдвое большим, чем для любой кривой, и соответствует двум проходам цикла из программы 20.1. То, что вы сейчас видите, связано с адресами регенерации динамической памяти, которые микропроцессор Z 80 генерирует в течение тактов Гз и Г4 операции извлечения КОПа (см. приложение). Такой адрес занимает 7 бит и увеличивается на 4 каждый раз, когда выполняется извлечение КОПа, при выполнении каждой команды. В нашем случае последовательность состоит из трех команд, так что уровень регенерации на линии Ло, который изменяется на противоположный при выполнении каждой команды, для возвращения в исходное состояние требует двух проходов цикла. Лабораторная работа 21. Микропроцессор IK Материал для чтения: гл. 11, разд. 11.1 -11.4, стр. 161-179, т. 2. Прочитайте описание этой работы и убедитесь, что понимаете программы. Задачи в основном тексте. Любое реальное приложение микрокомпьютера требует какого-то способа его коммуникаций с внешним миром. Один из таких способов - это разместить устройства ввода и вывода в пространстве памяти, так чтобы компьютер воспринимал их как память. Однако более удобным оказывается использование специальных команд IN и OUT, как это было описано в разд. 10.06 и 10.07. Чтобы продемонстрировать действие этих команд с минимальными изменениями в готовой схеме, мы можем в качестве устройства вывода использовать схему дисплея данных . Она уже соединена с шиной данных, поэтому нам остается только соединить ее вход ENABLE с линией IORQ процессора (вывод 20), и тогда содержимое накопителя будет выводиться на дисплей при каждом исполнении команды OUT. Поскольку при высоких тактовых частотах частота вывода данных окажется для нас слишком высокой, мы для собственного спасения должны отделить все команды OUT при помощи задерживающих циклов. Их использование представляет собой обычный прием в программировании ми крокомпьютеров. 21.1. Программа задержки. Этот прием часто используют Для того, чтобы осуществлять выполнение какой-нибудь операции через равные промежутки времени. Вместо того чтобы делать это при помощи специал^ьной дополнительной схемы, мы можем Инициировать регистр /? =100,0 X Уменьшить на 1 содер>симое регистра R=R-i  Остановиться Рис. 21.1. Блок-схема программы задержки; аспользовать программу, построенную, как показано на рис, 21,1. Запись такой программы для микропроцессора Z 80 - это программа 21,1. В качестве счетчика в ней использован регистр В, 00 06 64 MVI В, 100 ; загрузить 100 в регистр В . 02 05 LOOP; DCR В ; уменьшить В:В==В -1. 03 С2 02 00 JNZ LOOP ; перейти обратно, еслн результат еще равен нулю. В противном случае 06 76 HLT ; останов Программа 21.1. Программа задержки. Отметим использование нескольких входов в столбце данные (втором) для указания команд, имеющих более одного байта в длину; вследствие этого столбец адресов (первый) делает от строки к строке скачкн на одну, две или три ячейки за один раз. Убедитесь, что светодиодный индикатор соединен с выходом HALT (вывод 18) процессора, введите программу в память и запустите ее при помощи входа RESET. Остановится она сама. Команда DCR занимает 4 машинных цикла, команда JMP - 10. Поэтому весь цикл длится 10Х 14ХГ, где Т - тактовый период. Проверьте это при тактовой частоте 100 Гц. Переделайте программу (но не гактовую частоту!) так, чтобы задержка была равна в точности 10 с, и испытайте ее. Подумайте, как устроить задержку на 100 с при той же тактовой частоте (испытывать такую программу вам следовало бы при тактовой частоте 1 кГц). 2L2. Программирование ввода/вывода. Измените схему, как об этом говорилось во введении: отсоедините от земли вход ENABLE дисплея данных и соедините его с линией IORQ (вывод 20) процессора. После этого испытайте программу 21.2, которая представляет собой моднфицнрованную версию программы задержки. 00 Об 64 Begin: MVI В, 100 ; цикл задержки, как раньше 02 05 LOOP; DCR В 03 С2 02 00 JNZ LOOP 06 С6 XX ADI XX ; прибавить константу хх к накопителю 06 D3 00 OUT О ; вывести А в порт О (символический) OA СЗ 00 00 JMP Begin ; продолжать это повторять Программа 21.2. Программа для дисплея. Эта программа выводит иа дисплей через удобные интервалы времени последовательность шестнадцатеричных чисел, каждое из которых больше предыдущего на заранее заданную постоянную величину xxjg. Текущее значение содержится в другом регистре, в накопителе - регистр А. Испытайте программу при хх=03 и тактовой частоте 1 кГц. 21.3. Дешифровка кода устройства. Если число каналов ввода/вывода превышает единицу, приходится использовать какой-то способ дешифровки адреса, чтобы различать эти каналы. Во время выполнения команды IN или OUT на адресной шине (в продолжение сигнала низкого уровня на линии IORQ) присутствует код, называемый номером порта . Идентифицировать по этому коду устройство можно было бы при помощи комбинационных логических схем, однако более общим методом является использование дешифратора. Нам будет удобен дешифратор 74LS138, поскольку у него есть несколько разрешающих входов (два инверсных, один прямой). В следующей программе мы собираемся обеспечить возможность считывать состояние DIP-переключателя в накопитель, равно как и выводить его на дисплей данных, и для этого нам понадобится добавить еще одну схему (рис. 21.2). Не забывайте отсоединить существующую схему от входа ENABLE буфера переключателя DIP перед каждым выполнением программы и восстанавливать это соединение перед новым вводом данных. Переключатель DISPLAy SELECT (выбор дисплея) устанавливается в нижнее положение для ввода программ (или еще для наблюдения за шиной данных) и в верхнее положение, если дисплей надо использовать в 1Щ

E (буфер ввода данных) -E (дисплей данныи) Выбор дисплея Рис. 21.2. Дешифровка кода устройства при помоиш дешифратора 1x8 74LS138. Земля - вывод 8; U - вывод 16 качестве устройства вывода. При желании можно было бы заменить переключатель вентилем, управляемым сигналом BUSAK, тогда ата работа выполнялась бы автоматически; то же самое можно сделать и с входом ENABLE буфера переключателя DIP. В следуюохем выводе описаны оба порта В/В: Ввод/вывод Ввод Вывод X 0 0 0 0 X 0 0 0 1 Шестнадцатеричное число xOi Имя порта SWITCH (переключатель) DISPLA (дисплей) (х обозначает состояние, которое здесь не имеет значения) Теперь можно при помощи переключателей установить приращение (хх см. выше) во время выполнения программы. Соответствующая модифицированная версия - это программа 21.3. Операторы EQU в верхней части программы нужны ассемблеру, чтобы определить значения выбранных нами имен портов; этим строкам программы не соответствует ввод каких-либо данных, ; определить адреса портов ; как раньше ; ввести в накопитель состояние выключателей ; прибавить предыдущий итог в per. С ; см. 21-4 ниже / ; сохранить новый итог в С ; вывести новый итог ; повторить все сначала Программа 21.3. Программа для дисплея с вводимым с переключателя DIP приращением. 21.4. Десятичная арифметика. Держите питание включенным, чтобы сохранить вашу последнюю программу. Теперь замените NOP в адресе 09 на DAA (КОП 27i6) и снова запустите программу. Вы поражены? Команда DAA (десятичная коррекция накопигеля) воздействует на результат любой арифметической операции в накопителе. Она преобразует ответ к виду, который он имел бы, если бы операция проводилась наа упакованными двоично-десятичными (т. е. записанными по два десятичных разряда в байте) аргументами. На наших дисплеях этот формат выглядит как двухразрядное десятичное число. Чтобы все это осуществить, процессор для каждой арифметической операции сохраняет в виде флага Н результат переноса из бита 3 в бит 4; операция DAA, использовав значения Н и CY (бит переноса из бита 7) и содержимое накопителя, выводит результат. Вот вам

1 ... 53 54 55 56 57 58 59 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |