|

|

|

Разделы

Публикации

Популярные

Новые

|

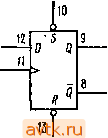

Главная » Сопряжение цифровых, аналоговых сигналов 1 ... 52 53 54 55 56 57 58 59 Последовательная логика 1 1S.3. />-триггеры. а. Уберите триггер 74LS107 и испытайте двойной £>-триггер 74LS74, Свяжите входы УСТАНОВКА и СБРОС с t/кк проверьте, что поданные на вход 0 данные устанавливаются иа выходе Q по положительному фронту тактового импульса. Теперь соедините Q с D, чтобы получить переключаемый триггер. Убедитесь, что он работает. Наконец, проверьте, имеют ли входы УСТАНОВКА и СБРОС приоритет над другими входами; для этого подайте устанавливающий сигнал на один из иих (т. е. соедините этот вход с землей) и после этого попробуйте опрокинуть триггер. Что

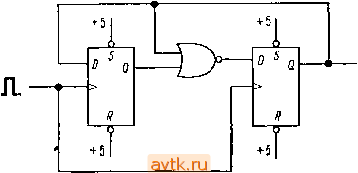

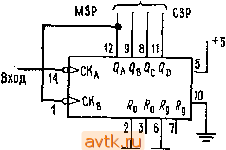

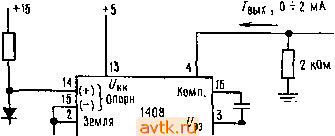

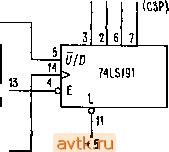

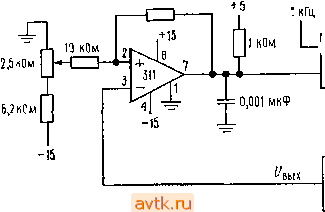

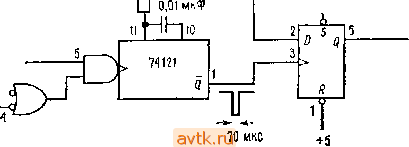

Г  Рис. 15.5. Дюйной О'Триггер 74LS74. Земля - вывод 7, I/rk ~ вывод 14. произойдет, если подать устанавливающие сигналы иа входы УСТАНОВКА и СБРОС одновременно (прежде чем ответить, убедитесь, что вы действительно проверили состояние обоих выходов Q и 0)? б. Соберите синхронную схему деления на три, которая изображена иа рис. 15.6 (рис. 8.52 в основном тексте). В качестве вентиля НЕ-ИЛИ можно взять либо одну из BbiKoa  1гтщ на 3 Рис. 15.6. Синхронный делитель на три иа триггерах 74LS74. секций микросхемы 74LS02 (двойной вентиль НЕ-ИЛИ с двумя входами), либо вентиль НЕ-И 74LS00, если его с умом приспособить к роли НЕ-ИЛИ. С помощью входов УСТАНОВКА и СБРОС установите счетчик в состояние, которое не может быть достигнуто в процессе деления на три, и убедитесь, что счетчик ие зависает в этом состоянии, когда на него поступает входной импульс. Выпишите полную диаграмму состояний. После того как проверите работу счетчика с помощью кнопочного выключателя и светодиодных индикаторов, испытайте его с тактовым сигналом 1 кГц и осциллографом. Нарисуйте на одном и том же листе бумаги сигналы, которые вы видите на выходах Qj, Qg и на входе, и добейтесь ясности в понимании того, как они связаны с процессом счета. 15.4. Счетчики СИС. а. Включите декадный счетчик 74LS90 для двоично-десятичного счета, как показано на рис. 15.7. Следует отметить, что эта ИМС состоит из двух секций, а именно из схемы деления на два, которая имеет свои выход и тактовый вход СКл и из схемы деления на пять (синхронный счетчик из трех триггеров) с тактовым входом СКв и выходами Qb-Qd- Чтобы получить двоично-десятичный счетчик, который делит на 10, надо их соединить, как показано на рнсунке. Подавайте на 1в M,6-J вход тактовые импульсы с кнопочного выключателя на макетной панели и наблюдайте за четырьмя выходными битами с помощью светодиодных индикаторов. После этого попробуйте, как действуют входы сброса и и прикиньте, для чего они нужны, Двоично-аесятичныЯ выход  Рис 15,7, Декадный счетчик 74LS90. Внимание Эта ИМС имеет необычное расположение выводов питания: вывод 5; земля-вывод 10. б. Теперь возьмите показанный иа рис. 15.8 дисплей (цифровой индикатор). Это очень удобный индикатор, поскольку он объединяет в себе фиксирующую схему (которая активируется входом EN), шестиадцатеричиый (0-9, A-F) дешифратор/ драйвер и собственно светодиоды дисплея. Соедините двоично-десятичиые выходы  Здесь видна ИМС Рис. 15.8. Дисплей 5082-7340 фирмы Хьюлетг - Паккард ( НР ). и дисплеи должны быть вставлены в специальные держатели, чтобы их хрупкие выводы не изгибались: используйте их только в таком виде. счетчика с входами А - D дисплея и пересчитайте все состояния счетчика. Наконец, попробуйте заменить счетчик 74LS90 счетчиком 74LS93, который делит на 16 (их вы-водысовместимы, но 74LS93 ие имеет 9), и повторите всю работу. в. Теперь посмотрите с помощью осциллографа, что происходит на каждом из выходов Qa-D счетчика 74LS93 в то время, когда на его вход подается тактовый сигнал с частотой 1 кГц, и проверьте, что на каждом следующем выходе частота в 2 раза меньше, чем на предыдущем. Затем проделайте то же самое для счетчика 74LS90 и объясните, что видите. Как можно было бы подключить счетчик 74LS90, чтобы получить на выходе симметричный прямоугольный сигнал с частотой, равной 0,1 тактовой? 15.5, Программируемый счетчик для деления иа N. Серия счетчиков 74LS160-3 состоит из двоичных синхронных 4-битовых (деление иа 16) и декадных (деление иа 10) счетчиков с синхронными Либо задаваемыми произвольно (асинхронными) сбросами. Для всех этих счетчиков предусмотрена возможность непосредственной параллельной синхронной загрузки (т. е. загрузки по переднему фронту тактового сигнала), которая разрешается по линии РЕ (parallel enable). Мы используем эту возможность, чтобы построить программируемый делящий на N счетчик, схема которого по- Логика трех состояний казана на рис. 15.9. N*, т. е. первое дополнение N, подается на параллельные входы ввод с которых разрешается, когда на выходе ТС (terminal count) оказывается сигнал высокого уровня (15 для двоичного счетчика и 9 для десятичного); при этом в счетчик загружается N*, и все начинается сначала. Испытайте эту схему при различный значениях N. СЕР OoQiQi-Qj ТС СЕТ > R DDDiD РЕ Рис. 15.9. Схема деления на N, использующая синхронный двоичный счетчик 74LS16I, 15.6. Секундомер. Последним упражнением этой работы будет построение секундо* мера; как это сделать, предлагается на рис. 15.10. Используйте сигнал 100 Гц (делен* ный на 10 тактовый сигнал частотой 1 кГц с макетной панели), введенный в 3-разрядный счетчик, выходные биты которого соединены с индикаторами. Вводом в З-разцййныи дисплей

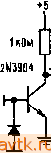

с > 3 - разрядный Выключатель сброс сброс Рис. 15.10. Блок-схема секундомера. счетчик управляйте посредством выхода триггера в счетном режиме, который в свою очередь управляется кнопочным выключателем (защищенным от дребезга контактов) на макетной панели. Еще один выключатель используйте для сброса счетчика. Не забудьте сообразить, что надо сделать с различными входами, сбросами, тактовыми, разрешающими и т. д. Все вместе займет у вас около часа, так что не начинайте эту работу, если не хватит времени ее закончить. Лабораторная работа 16. Логические схемы с тремя состояниями Материал для чтения: гл. 8, разд. 8.26 и до конца главы, стр. 569-596, т. 1. Задачи: дополнительные упражнения 9, 10, 13. В этой работе мы займемся устройствами с тремя состояниями и используем их в уии кальной схеме моношина (уникальной поскольку надо быть безумцем, чтобы по- строить такую схему для употребления в реальной жнзнн!), 16.1. ТТЛ-буф^) с тремя состояниями. В лабораторной работе 14 мъ видели, что добавление входа ENABLE превращает вентиль ТТЛ в схему с тремя состояниями. Теперь посмотрите в приложении, как расположены выводы счетверенного буфера с тремя состояниями 74LS125. Эта микросхема имеет четыре независимых иеинверти-рующих буфера с отдельным разрешающим входом (ENABLE) каждый. Для разрешения выхода на входе ENABLE должен быть сигнал низкого уровня; для переключения схемы в разомкнутое ( высокое Z ) состояние на этот вход надо подать сигнал высокого уровня. Чтобы испытать такой буфер, сначала отоприте одну из секций микросхемы и проверьте, что ее выход следует за входом (используйте для этого светодиодные индикаторы и переключатели). После этого заприте ее и проверьте, что потенциал выхода может быть задан извне путем подачи извне через сопротивление 2,2 кОм -f-5 В или землю. При этом выход переходит в состояние с высоким или низким уровнем. 16.2. Моиошина - пример шины данных. Оставшуюся часть этой лабораторной работы мы собираемся посвятить конструированию шины данных, в которой будут использованы буфера с тремя состояниями. Шина - это система совмещенных линий связи, питаемых от одного или нескольких источников данных, причем для предотвращения соревнования на шине должны выполняться необходимые соглашения относительно протокола. Для ознакомления с темой обратитесь к основному тексту, стр. 522 (рис. 8.19). Главы 10 и 11 полны упоминаний о шииах, и мы еще встретимся с ними в следующих лабораторных работах. 11!ГЦ-

д -А Дисплей А в с D Цифра установлена бит \становлен 74LS164 ЛгАгАгА, Кнопочный выключатель, защищенный от - дребезга онтатов 7-115125 За в ffc 74ls90 Рис. 16.1. функциональная диаграмма моношины . На этот раз нахождение нужных выводов н решение вопроса, что делать с ненужными, мы оставляем читателю в качестве упражнения. Простой, но нетривиальный пример использования шины показан иа рис. 16.1. Счетчик 74LS90 внизу рисунка, управляемый кнопочным выключателем, будет служить нам источником данных. Для передачи двоично-десятичных данных на дисплей (на рисунке справа) мы используем однобитовую шину, подавая на иее каждый из битов по очереди, в порядке Qjy, Qc, Qb, Qa< через буфера 74LS125. Эта передача производится с частотой 1 кГц с помощью 2-разрядного счетчика (74LS93) и дешифратора 1 на 8 (74LS138), который по очереди отпирает каждый буфер. Сдвиговый регистр (74LS164), расположенный на противоположном конце рисунка, принимает биты по переднему фронту импульса BIT VALID (бит установлен), который используется здесь как тактирующий. Из 8 бит этого типа мы используем только 4. Дисплей фиксирует поступившую таким образом двоично-десятичную цифру с помощью импул-ьса CHAR VALID (цифра установлена), который выдается один 74LSI38 входы С, D, ENABLE и ENABLE? 74LS90 тактовый вход СКд? входы Rn и 9? 74LS164 вход СБРОС? второй последовательный вход? Теперь попробуйте запустить вашу схему. Очень возможно, что она будет действовать сразу. Если это случится, придумайте разумную процедуру поиска неисправностей и выясните, что действует неправильно. Существуют два популярных подхода к этой проблеме: 1) Проследить по очереди действие всех ИМС, начиная от входа схемы (т. е. синхросигнала и кнопки) по направлению к ее выходам (т. е. дисплею). 2) Начиная с выхода, размыкать схему между двумя ИМС и вводить в место разрыва логические уровни, проверяя, правильно ли отвечает иа них выход (в нашем случае дисплей). Как правило, это делается для отдельных линий, по одной за один раз; продвигайтесь по направлению к входу, пока не встретите неисправность. Лабораторная работа 17. Преобразование аналогового сигнала в цифровой Материал для чтения; гл. 9, разд. 9.01-9.08, стр. 5-25, разд. 9.18-9.19, стр. 50-51, разд. 9.23 (двухстадийное интегрирование), стр.64, т. 2. Задачи: упражнение 9. (; дополнительные упражнения 1,2; примеры негодных схем. Здесь будет рассмотрена техника цифро-аналоговых преобразований. Мы рассмотрим 8-битовый ЦАП с токовыми ключами (микросхема 1408) и с токовым выходом и затем, включив его в цепь обратной связи, построим следящий АЦП. Монтируйте схемы аккуратно; каждый этап работы основан на использовании предыдущей схемы. 17.1. Цифро-аналоговый преобразователь, а. Начните с подключения двоичного ре-версивного синхронною 4-разрядного счетчика 74LS191. По поводу расположения выводов счетчика см. приложение В. Фиксируйте на входе ENABLE сигнал низкого, а на входе LOAD - высокого уровня. Выходы соедините со светодиодными индикаторами и тактируйте микросхему от защищенного от дребезга контактов кнопочного выключателя (используйте выход с нормально высоким уровнем). Проверьте работу счетчика в режимах суммирования (низкий уровень на входе U/D) и вычитания (U/D - высокий уровень). б. Теперь используйте выход счетчика, чтобы задавать данные для ЦАП 1408 (рис. 17.1). Соедините выходные разряды счетчика (их четыре) со старшими разрядами (т. е. выводами 8, 7, 6, 5) ЦАП. В каком порядке их следует соединять? Тактируйте счетчик сигналом частотой 1 кГц с макетной панели. Сигнал какой формы должен получиться на выходе ЦАП? Посмотрите его иа осциллографе Теперь измените направление работы счетчика; при этом получится другая ступенчатая кривая. раз и а каждые четыре бита. Имеет ли значение то, что сдвиговый регистр не сбрасывается после фиксации данных дисплеем? Начните с того, что возьмите лист бумаги и начертите временную диаграмму, поместив на ее верхней линии синхросигнал с частотой 1 кГц. Отметьте на диаграмме состояния счетчика 74LS93 и выходов дешифратора 74LS138h три сигнала на шине; используйте формат вроде того, в котором выполнен рис. 8.55, б на стр. 553 основного текста. Когда вы будете уверены, что ие возникнет никаких проблем с соревнованиями на шине или с гонками логических состояний, вы будете готовы к сборке схемы. Теперь сообразите, как следует поступить со всеми входами, которые специально не обозначены на рис. 16.1; мы нарочно их пропустили, чтобы эти упражнения было читать труднее, чем поваренную книгу. Посмотрите приложение В (расположение выводов). В частности: 74LS93 тактовый вход СК? входы Rf7 в. Добавьте второй счетчик 74LS191, как это показано на рисЛ7.2. Выход RCO (ripple carry output) - выход переноса использован, чтобы осуществлять перенос: на выводе 13 сигнал имеет низкий уровень, когда счетчик находится в состоянии, со- 7,5 кОм  4г -кг J?hllOl 9 8 7 б| 5 ] 270 пФ (МЗР) Вход данных (СЗР) Рис, 17.1, Монолитный 8-битовый цифро-аналоговый преобразователь 1408 с токовым выходом. Токовый выход преобразуется в выход по напряжению с помощью сопротивления 2 кОм. Обратите внимание на полярность выхода, ответствующем последней ступени счета (15 для режима суммировани и О для режима вычитания); этот вывод соединен с входом ENABLE (разрешение) второй ступени, которая, таким образом, делает следующий шаг по следующему тактовому импульсу. Соедините все разряды с входами ЦАП 1408 (в каком порядке?) и посмотрите на новую ступенчатую кривую, которая теперь больше похожа на наклонную линию, 8-битовый выход /ч Тактовый вход U/D Е  Рис. 17,2. Полностью синхронизованный 8-битовый реверсивный счетчик, исполь-йующий два счетчика 74LS191. 17,2. Следящий аналого-цифровой преобразователь, а. Теперь мы можем добавить схему компаратора и получить следящий АЦП, как это показано на рис. 17.3, Подробности можно узнать из разд, 9,22 (стр, 60, т. 2). Потенциометр 2,5 кОм играет роль аналогового входа. Компаратор 311 сравнивает напряжения на этом входе и на выходе ЦАП и переводит счетчик в режим (суммирования или вычитания), нужный, чтобы согласовать выход ЦАП с аналоговым входом. Состояние счетЧика служит при этом цифровым выходом АЦП. Выведите на дисплей (светодиодный дисплей с дешифратором фирмы Hewlett - Packard), как показано на рисунке, четыре старших разряда счетчика. Медленно проверните потенциометр в обе стороны до упора. Что происходит вблизи крайних положений потенциометра? Как это объяснить? Теперь проверьте напряжение на выходе ЦАП 1408; оно должно плясать меж-у двумя соседними уровнями лестницы . Попробуйте двигать потенциометр быстро; вы должны заметить скачки напряжения с еще большей амплитудой, которые появ* id mum  сметчик Ш 1408 и Рис. 17.3. Следящий АЦП, использующий 8-битовый счетчик, и ЦАП из разд. 17.1. Добавление схемы гистерезиса и емкости (что снижает скорость переключения) к компаратору 311 имеет целью уменьшить склонность этой схемы к генерации. ляются только во время движения потенциометра, но не в то время, когда ЦАП скатывается к своему новому состоянию. Причиной таких скачков является ошибка в последовательности счета счетчика 74LS191, которая возникает, t ели изменить уровень сигнала на входе U/D в то время, корда тактовый сигнал имеет низкий уровень. В технических условиях на микросхему 74LS191 скачано, что состояние входов U/D и ENABLE не должно меняться в течение всего того времени, когда иа тактовый вход подается сигнал низкого уровня, и это условие может быть нарушено, если (быстрое) изменение аналогового входа заставит выход компаратора изменяться между тактовыми импульсами. Нарисуйте временную диаграмму для так овых импульсов и выхода компаратора, и вы убедитесь, что это действительно ак. б. Отсоедините четыре младших разряда на входе ЦАП 1408, чтобы лучше видеть, как пляшет АЦП в установившемся режиме. Теперь на экране осциллографа только 16 уровней, и выход ЦАП всегда колеблется между двумя из них. 10 КОМ Выход компаратора +5  Тактовый 3 1/2 шт Рис. 17.4. Средство против нарушения условий синхронизации, с которым мы столкнулись выше. в. Средство для решения проблемы ошибки в счетной последовательности, с которой мы встретились в пункте 17.2 (а), предложено на рис. 17.4. Состояние выхода компаратора снимается на запускаемый по фронту триггер (74LS74) в то время, когда тактовый сигнал наверняка имеет высокий уровень. Одновибратор (74121) задерживает на 70 мкс положительный фронт тактового импульса, чтобы позволить установиться выходам ЦАП и компаратора; без него схема была бы более изящной, но тогда наш АЦП при осуществлении поиска сдвигался бы на 3 шага вместо од- ного. Это последнее утверждение вы должны объяснить. Испробуйте это средство. Если сначала устройство не будет действовать, проверьте, работает ли одновибратор. Теперь выход АЦП будет свободен от всплесков. Лабораторная работа 18. Последовательная логика II Материал для чтения: гл.9, разд. 9.28-9.39, стр. 78-104, т. 2. Не беспокойтесь о математических подробностях, они могут вас запутать. Задачи: упражнение 9.4, дополнительное упражнение 4. 18.1.. Геяератор псевдослучайной последовательности битов. Эта схема представляет собой стандартный генератор ПСПБ из разд 9.34 с максимальным числом ступеней регистра сдвига, равным 16. Второй вентиль (Исключающее ИЛИ) изменяет знак обратной связи, так что схема не может застрять в положении со всеми нулями, которое в противном случае было бы ее единственным устойчивым.состоянием (вместо него таковым является состояние со всеми единицами); в этом случае, если нужно, генератор можно запустить снова при помощи входа СБРОС. Для проверки этого утверждения рассмотрите эволюцию состояния со всеми единицами (см. стр. 104). 4,7 ком 1N914  бит п Бит т 1 2 5 4 5 6 7 8 6 iDhl 1213 Син*р 74LS164 9 10 111113 14 1516 N бит 74 LSI 64 1hOm- 100 Om T iJ I Громкоговоритель Рис. 18,i. Генератор псевдослучайной последовательности. ИМС 74LS86 и 74LS164 имеют стандартное угловое расположение выводов питания. Подайте на тактовый вход от генератора функций прямоугольный сигнал боль-июй амплитуды частотой 100 кГц. Для начала установите значения т=15, д=14 (максимально возможная длина ПСПБ) и послушайте через громкоговоритель шум на выходе; этот шум должен быть белым , т. е. ои не должен иметь каких-либо отличительных свойств или заметной частоты. Единственная существующая здесь периодичность - это повторяющаяся длина последовательности. Подсчитайте время этого повторения. Можете ли вы его услышать? Затем попробуйте задать т=15, л=16 и /и=15, л=13. Ни одна из этих комбинаций не дает последовательность максимальной длины. Испробуйте также и другие комбинации 1кОм Бит 16 К осциллографу : 0.01 м Ф Рис. 18.2. Фильтр низких частот для генератора ПСПБ. Подключите показанный на рис. 18,2 фильтр к одному из выходов нашего генератора. Почему все равно к какому? Теперь тактируйте схему с частотой 1 МГц и наблюдайте пействие фильтра при помощи осциллографа Объясните общий смысл увиденного в терминах тактовой час готы и /здб фильтра, Осторожно запустите Последовательная логика П развертку самым высоким или самым низким пиком последовательности; это возможно даже для последовательности максимальной длины. Вместе с полученной кривой выведите на экран осциллографа кривую выхода без фильтра. Найдите самые длинные последовательности повторяюшихся единиц и нулей. Объясните, исходя из длины регистра сдвига, почему длины этих последовательностей именно таковы. Каким характерным особенностям отфильтрованного выхода они соответствуют? Теперь выключите или сделайте очень медленной горизонтальную развертку осциллографа. Кривая для отфильтрованного выхода при этом выродится в вертикальную линию неременной яркости. Яркость каждого участка этой линии пропорциональна облему количеству времени, которое выход проводит при соответствующем Значении напряжения. Опишите в общих словах распределение, которое вы видите; какое распределение оно аппроксимирует? 18.2. Умножитель частоты с цепью фазовой автоподстройкн. Соберите схему, показанную на рис. 18 3 Установите генератор сигнала на входе на частоту ровно 60 Гц, 2N39Q4 4.7 вОм + 15 1 кОм 6В0 пФ 4046 4,3 МОм 1 мкФ ф 33Q rQm 4046 5L 200 кОм !0 нОм fill (? 0,0?9 58?;(?6 4020 Рис. 18 3. Умножитель частоты нз схеме КМОП ФАПЧ 4046. Эта схема основана на ряо. 9.58 в тексте. Вывод \b=UQQ = 15 В н вывод 8==LfnH = авмля для обоих ИМС Фазовый детектор и ГУН схемы 4046 нарисованы как отдельные блоки для чего придется использовать лабораторный частотомер, работающий в режиме измерения периода. Чему должна быть равна частота на выходе ГУН * (вывод 4 микросхемы 4046)? Теперь измерьте ее частотомером. Исследуйте также поведение одного из промежуточных выходов микросхемы 4020. Теперь посмотрите иа выход фазового детектора (вывод 13 микросхемы 4046). Это - детектор типа II в соответствии с классификацией разд. 9.29 (стр. 80), Вы увидите строчку коротких (но ие нулевой длины) положительных движущихся импульсов. Теория предсказывает, что в установившемся режиме они должны исчезать, но нагрузка (Ю МОм) пробника осциллографа, который вы используете, позволяет конденсатору фильтра разряжаться до такой степени, что они появляются. Вставьте между конденсатором и пробником повторитель 355, и они пропадут Медленно подстраивая входную частоту, следите за выходом детектора. Теперь что-нибудь проясняется? Сейчас постоянная времени фильтра точно подобрана для входной частоты 60 Гц. Исследуйте, к чему приводит изменение некоторых величин, в частности замените сопротивление 330 кОм на 33 кОм и проследите, как ФАПЧ будет колебаться вверх и вниз перед тем, как установится правильная частота. Это зрелище впечатляет! Наконец, испытайте детектор типа I, который тоже содержится в микросхеме 4046. Его выход - это вывод I, а входы совпадают с входами детектора II, так что * Геыердтор, управляемый напряжением,- Прим, перев. вам понадобится только переключить один провод с вывода 13 на вывод 1. Тогда вы сможете увидеть флюктуации частоты ГУН, зависящие от периода входного сигнала; их можно увеличить, уменьшив величину (1 мкФ) емкости фильтра цепи обратной связи. Если вы будете резко менять входную частоту, то сможете также поймать ее гармоники. Лабораторная работа 19. Микропроцессор I -135, т. 2. Материал для чтения: гл. 10, разд. 10.1-10.11, стр. 114- Задачи: дополнительные упражнения 1-6. Эта серия состоит из пяти лабораторных работ, каждая из которых опирается на предыдущие. Первые две работы посвящены сборке ЭВМ, а остальные три - это замкнутые в себе эксперименты с ее использованием (поэтому их можно проводить в любом порядке). Вот темы этих лабораторных работ: Работа 19. Шииы адресов и данных. Память Работа 20. Центральный процессор. Тестирование и характеристики Работа 21. Способы синхронизации и организация простого ввода / вывода. Десятичная арифметика Работа 22. Частотомер (Работа 23. Методы аналоговых преобразований. Простые графики Теперь посмотрите на рис. 19.1. На нем изображена блок-схема компьютера, который мы собираемся построить. Мы здесь использовали популярный микропроцессор Z80, так как он имеет статические регистры; это позволит нам работать с небольшой тактовой частотой, чтобы можно было проследить выполнение отдельных команд.

Интерфейс В/в пттгп Внешний мир

Рис. 19.1. Блок-схема компьютера. Для удобства мы ограничимся системой команд микропроцессора 8085, к которой мы привыкли, читая гл. И; эта система является частью полной системы команд микропроцессора Z80 и полностью с ней совместима. Если вы когда-нибудь обратитесь к литературе, относящейся к Z80, вам придется привыкать к другим мнемокодам (КОПы и здесь, естественно, те же самые); если вы это проделаете, то сможете воспользоваться преимуществами, которые дает расширенная система команд, хотя для выполнения наших лабораторных работ это не обязательно. Прежде чем начать работу, примите к сведению несколько общих советов: 1) Монтаж должен быть очень аккуратным. Соединения делайте возможно более короткими и снабжайте их цветной маркировкой; впоследствии вы поймете, насколько полезной может оказаться такая привычка при поиске ошибок. Особенно полезно использовать разные цвета для каждого бита шины, поскольку случайные лерестанов- 1 ... 52 53 54 55 56 57 58 59 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |