|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Сопряжение цифровых, аналоговых сигналов 1 ... 20 21 22 23 24 25 26 ... 59 ботает от одного источника питания +5 В и стоит около 25 долл. Для его программирования надо приложить постоянное напряжение +25 В к программирующему выводу, после чего записывать нужные данные со скоростью 1 байт в 50 мс, проверяя, правильно ли он записан. На всю работу уходит при этом 100 с. Более старая ИМС2708 имеет вдвое меньшую емкость, требует трех источников питания (+12, +5 и -5 В) и стоит около 5 долл. УФППЗУ - это основной тип ПЗУ для небольших систем и для устройств частного применения. Для макетирования они просто замечательны. Электрически перепрограммируемые ПЗУ (ЭППЗУ). Эти ПЗУ могут быть запрограммированы и очищены электрически, не нуждаясь в растянутой процедуре стирания, присущей УФППЗУ. На примере ЭППЗУ можно наблюдать процесс появления новой технологии ПЗУ. Это новое направление обещает значительное продвижение в отношении плотности упаковки и удобства использования. П.И. Конструирование системы на БИС Мы рассмотрели периферийные СИС и БИС, различные типы ЗУПВ и ППЗУ. Теперь было бы поучительно увидеть, как из этих типов памяти и вспомогательных схем составляется небольшая система. Мы покажем, как можно смешивать ЗУПВ и ПЗУ, как включаются в систему периферийные приборы и как добавлять к ней ИМС памяти, которые не сконструированы специально под микропроцессор . Многоцелевой микропроцессорный модуль. Взгляните на рис. 11.22. Этот чертеж мог бы быть проектом готового к выпуску прибора. Тем не менее, пока не раскрыто содержимое ПЗУ, невозможно сказать, что делает этот при-бор. Такая схема имеет более общий характер чем, например, приведенная на рис. 11.4, поскольку она содержит многоцелевые программируемые многоканальные порты В/В, имеет расширяемое пространство ПЗУ, устройства для последовательного ввода/вывода данных и место (возможность) для подключения дополнительных ЗУПВ. Мы начали с нашего излюбленного микропроцессора 8085. Затем мы взяли две ИМС 8155 параллельного ввода/вывода (ПВВ), которые нужны в качестве параллельных портов для обмена данными с внешним миром, а также в качестве таймера для программирования скорости передачи информации в УСАПП 8251. Кроме того, каждый из них содержит по 256 байт ЗУПВ, что дает возможность в небольшой системе обойтись без других дополнительных ЗУПВ. УФППЗУ (чип 2716) располагается в начале ( на дне ) памяти иусодержит инициирующие программы и специальную программу нашего прибора. Вся система невелика и компактна: в неивсето три корпуса с 40 выводами, двухрядный корпус с 28 выводами, еще один корпус с 24 выводами, два малых корпуса DIP, одно сопротивление, один конденсатор и один кристалл резонатора. Все вместе на печатной плате могло бы показаться достаточно невыразительным. Вся 8 №62 система была бы построена с применением только БИС если бы она не нуждалась в фиксирующей схеме для задания младшей половины ♦ g-IRDY Ш МГц 50В5 s\ Прерывания HOLD INTR TRAP 5,5 6.5 7,5 7> 6 > xlz 3 0 [Дополнительные ПЗУ Г LS373 L Адреса/данные 3,072 МГц 1мкф -к Внлючмив CS PD К 27)5 Л гк ln cnnav AD-ABi PD WR 4C£ 8155 <3RD Параллельный ввод/ выбоа ш С/а Снсрость информации са: £Q 01 РйС. 11.22. Схема микропроцессора общего назначения. адреса СППЗУ (надо помнить, младшие разрядьт адреса итеремешаны с данными на шине данных) и в- дешифрш-оре для раэдежйИ5Р яамяти в соответствии со старшими битами адреса. УФПШУ пшещено в 3000 h 2800 F i 2000 F  1 vann i 3Vn6 -2. 255 бант i 3Vnb-I, г56 6айг 1800 I------[ 1000 1----- 08П' , Дополнительные сппзу 0000 2K ПЭ-У cnnav, гОв байт niaH пространства памяти самом начале памяти ввиду того, что при включении процессор 41чи-нает выполнять программу, начиная с нулевой ячейки (как уже бшо об этом сказано). Кроме того, прерывания осуществляют принудительные обращения к расположенным вблизи начала памяти ячейкам (2С, 34 и ЗС, все шестнадцатеричные), ffpf так что для операций с ними желательно расположить всю программу также в начале памяти. Дешифратор 1-8 (74LS138) помещает УФППЗУ в первые 2К памяти, причем его остальные выходы можно использовать для тех трех дополнительных чипов ПЗУ, в ненужности которых БЫ сейчас абсолютно уверены и которые неизбежно вам понадобятся. Чтобы разрешить обращение к ПЗУ, адресный бит А13 должен быть установлен в НИЗКИЙ уровень; если А13 установлен в ВЫСОКИЙ уровень, обращение к ПЗУ запрещено, и выходы дешифратора 74LS138 выбирают периферийные устройства (УСАПП и ПВВ). План размещения памяти нашей системы приведен на рис. 11.23, Некоторые дополнительные замечания: заметим, что не обязательно заполнять пространство памяти непрерывно, без просветов, начиная с ее начала. Назначение отдельных блоков памяти в соответствии с имеющимися в наличии старшими адресными линиями, как мы это сейчас сделали, часто упрощает схему. [Дели в пространстве памяти, которые при этом получаются, ничему не мешают. Заметим также, что, оставив свободными несколько выходов дешифратора и не полностью проведя дешифровку адресных битов процессора 8085, мы разрешили доступ к периферийным устройствам из многих мест памяти, удаленных от ее начала, точно так же, как это было в примере с 6-канальным счетчиком (см. рис. 11.6). Еще одна тонкость в нашем примере связана с адресацией периферийных схем. Поскольку возбужденные выходы (74LS138) не следят за линией ДОУМ процессора, они разрешают обращение к периферийным приборйм при выполнении команд кш. квода/вывода, так и обращения к памяти. Это, однако, не приводит к ошибкам, поскольку за линией Ш/М' следят ПВВ 8155 (которые сами выбирают между своей функцией ввода/вывода и об- 20 28 20 -8Z5f -8155U} -8155(1) План пространства ввода/вывода Рис. 11,3. Размещение памяти для схемы микропроцессора общего назначения. ращением к памяти), а УСАПП просто появляется в одних и тех же ячейках пространства памяти и пространства В/В. Упражнение 11.12. Использовать добавочные выводы для осуществления полной дешифровки адреса, так чтобы ЗУПВ и СППЗУ не появлялись многократно в про-странстве адресов. Дополнительная память: вопросы синхронизации. Во многих приложениях тех 512 байт, которые нам предоставляют ПВВ в предыдущем примере, просто не хватает для хранения данных, с которыми надо оперировать. Примером может служить устройство (буфер) для приема взрывов данных, поступающих, скажем с блока магнитной L5I5B LSD8 WR Ar доропнительные 3VnB

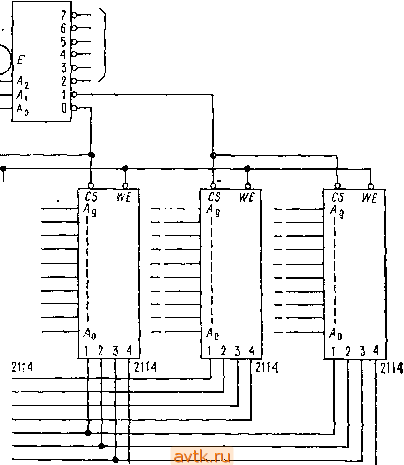

AB---J , Рис. II 24. Добавление ЗУПВ 2114 на 2Кбайт к схеме микропроцессора общего яаз начения. ленты или диска. Для такого приложения ЗУПВ должно иметь достаточную емкость для записи целого блока поступающих данных, которые затем обрабатываются и пересылаются дальше до прихода следующего взрыва , Было бы соблазнительно использовать здесь одно из дешевых и популярных ЗУПВ, такое, как, например, вездесущая 2114, поскольку ЗУПВ, разработанные специально для совместной работы с микропроцессором, обычно значительно дороже. Например, 1К байт памяти, составленный из двух ИМС 2114, обойдется приблизительно в 8 долд., в то время как ЗУПВ 8185 с такой же емкостью, предназначенное специально для использования с микропроцессором 8085, стоит около 25 долл. При добавлении ЗУ, не сконструированных специально для работы с данным ЦП, приходится, вообще говоря, добавлять также и некоторые другие внешние схемы для формирования стробирующих и разрешающих сигналов. Кроме того, всегда надо следить за соблюдением условий синхронизации (это касается, например, времени установки и времени обращения). На рис. 11.24 показано, как добавить 2 Кбайт памяти к нашей первоначальной схеме. Дешифратор 74LS138 отпирается только при установке адресного бита А^ в ВЫСОКИЙ уровень, т. е. ЗУПВ размещается в пространстве адресов, начиная с ячейки 4000 Н. Для того чтобы с выходов схемы 74LS138 был подан отпирающий сигнал на входы CS (выбор чипа) надлежащей пары ЗУПВ 2114, на два других отпирающих входа 74LS138 должны поступить стробы доступа к памяти (НИЗКИЙ уровень на линии 10/М') и считьшания или записи. При помощи такой схемы к системе можно добавить ЗУПВ с общей емкостью до 8 Кбайт. Ситуация, которая возникает при этом в связи с синхронизацией работы системы, изображена на рис. 11.25, где требования, предъявляемые процессором и памятью, показаны относительно одной и той же оси времени. Полный адрес фиксируется и передается в ЗУПВ в конце импульса ALE (или раньше, если для фиксации младшего байта адреса использован регистр следящего типа), а полученные в ответ из ЗУПВ данные должны быть установлены на шине в течение не более чем 460 НС после прохождения его заднего фронта; последнее условие необхсГдимо, чтобы обеспечить нужное для процессора время установки (100 не) до того, как окончится импульс RD. Временная диаграмма для ЗУПВ 2114 также приведена на рис. 11.25; сущест-I венным здесь является то обстоятельство, что данные окончательно устанавливаются только через 450 не (/а, время доступа) после того, как установился адрес. Если для фиксации младшего байта адреса использована запускаемая по фронту фиксирующая схема, возможность I выполнить условие за время установки оказывается почти упущенной, поскольку ЗУПВ забирает 450 не для доступа к своим данным, в то время так ЦП навязывает крайний срок в 460 не. Фактически это ус-J ловие оказывается даже нарушенным на 24 не, так как фиксирующая схема имеет еще и задержку распространения, равную (максимально) 34 НС. Мы, к счастью, использовали следящий регистр, который проводит через соответствующее установившемуся адресу состояние при- близительно за 100 не до окончания импульса ALE и тем обеспечивает , резерв 75 НС Аналогичный подсчет для цикла WRITE также показал бы наличие достаточного резерва времени. Отметим, что ЗУПВ 2114 заведомо успевает убрать свои данные с шины адресрв/данных до того, как ЦП снова подаст на нее адресную информацию в начале еле* дующего машинного цикла, так что на этой шине не происходит споров перекрывающихся сигналов. Запас времени в данном случае составляет 50 НС. Кристалл 6,1И Mti; /-V y-\ 7-\ Старший 1пит *~\r ?дрсса - Мплцинш Www ,lAiUU\ АН J v. Л ARpec 3VnB, вывод данных Выбор чипа 460 не 400 НС -300 НС-* U,n,c4WTMBaHwe данных. шины ЦП; 100 НС VcTa- 150 НС *-> Aftpec \(стано8пен Данные установлены Сигналы зупв ?1И вршя доступа 450 не [макс.) tea ь'бор чипа.выхац установлен, 120 нс(мзкс4 г'г.д! отключение выбранного чипа, tOO не 1ма,1\с) Рис. 11.25. Диаграмма синхрониаации обращения к памяти для машинного цикла READ процессора 8085 при использовании ЗУПВ 2114. Два примечания: в наших оценках всегда использовались наихудшие из возможных значений. На самом деле схема с запускае-емой по фронту фиксацией адреса, вероятно, могла бы прекрасно работать. Кроме того, мы использовали самые медленные схемы из семейств 2114 и 8085; дополнительные резервы времени всегда можно получить, перейдя к использованию более быстродействующих разновидностей схем или понизив тактовую частоту системы. О емкостях. Все связанные с синхронизацией технические условия в описаниях устройств указываются применительно к некоторой предполагаемой емкостной нагрузке. Все наихудшие значения в предыдущем примере задаются в предположении, что емкостная н^- MuKponpouficcopbi 231 Грузка на всех линиях составляет 150 пФ. Для системы, состоящей из дюжины или более ИМС, имеет смысл проверить, действительно ли суммарная емкостная нагрузка не превышает 150 пФ; в противном случае указанные технические условия необходимо откорректировать в соответствии с формулами, приведенными в описании микропроцессора (такое описание всегда представляет собой целую книгу, и часто довольно толстую). Ситуация с емкостными нагрузками в случае предыдущей схемы складывается следующим образом:

Выходит, что емкостная нагрузка приближается к указанным в описании 150 пФ, если учесть емкость монтажа. Ясно, что наша небольшая система не может быть заметно расширена без использования буферов для увеличения мощности сигналов ЦП. С другой стороны, с участием всех необходимых ИМС схема может разрастись до такой степени, что окажется не подходящей для размещения на одной печатной плате. На этом этапе мы могли бы начать думать о размещении системы на нескольких платах с разъемами для соединения с общей панелью (или с задней стенкой), контакты разъемов которой соединены с общей шиной. Некоторые из популярных шин для микропроцессоров мы рассмотрим в следующем разделе. С применением буферов для усиления сигналов ЦП связана од- на интересная тонкость: поскольку шина данных (ADo-AD) -явля- ется двунаправленной, буфер должен обладать способностью передавать сигналы в обоих направлениях, хотя и не обязательно одновре-- менно. Это легко осуществимо с помощью такой ИМС, как восьмика- нальный приемопередатчик для шин 74LS245, который состоит просто из пары встречно включенных буферов с тремя состояниями на каждой сигнальной линии. На рис. 11.26 показано соединение ЦП 8085 с такими шинными буферами. Линии ADo-AD, нормально включены .для питания шины (74LS245 в режиме передачи), а переключение бу-; фера в приемный режим производится только на то время, пока длится ; подаваемый из ЦП импульс RD. Остальные линии являются однона-I правленными и обслуживаются обычными шести- и восьмиканальны-; ни буферами. Заметим, что линии RD, WR и 10/М' преобразованы в систему из четырех управляющих линий, что делает необязательной дешифровку на каждой отдельной плате. Естественно, что в большой системе, в которой линии основной панели нагружены значительными емкостями, приходится использо- вать буфера и для сигналов, идущих с другого конца линии \ При этом для линий данных на плате памяти надо было бы использовать буфер для двунаправленной передачи, направление которой управлялось бы по линии MEMRD; вероятно, следовало бы поставитьбу- 8085 Щ RD WR JO/M CLK Включение р i S 244 LS373 Двунаправленный драйвер DIR ОЕ L5 245 Драйвер LS 366 -с > > > > Рис, 11.26. Использование буферов на шине ЦП 8085. Данные В/В MEMRD MEMWR 10RD Управление ТШ К фер и на входных адресных линиях этой платы, поскольку они создают большую емкостную нагрузку на шину. Максимальную нагрузку, ч То есть не от микропроцессора, а от других устройств системы.- Прим. перев. которую плата может создавать на любой шине, обычно каким-нибудь способом обозначают в спецификации этой платы, например как двойную нагрузку схемы 74LSxx. ДАЛЬНЕЙШИЕ АСПЕКТЫ КОНСТРУИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ 11.12. Шина S100 Историческая справка. Конструкторы первого микропроцессорного набора MITS Altair 8800 были первыми, кто столкнулся с задачами, которые мы сейчас обсуждали. В их статье в Popular Electronics за 1975 г. на фотографиях и схемах была изображена собранная на винтах с проставками этажерка из печатных плат, соединенных друг с другом набором проводов, впаянных в выставленные друг над другом отверстия на платах. К счастью, конструкторы не остановились на этом непрочном сооружении, и заказчики получили набор Altair 8800 с основной панелью, заселенной разъемами на 100 выводов для подсоединения торцов отдельных печатных плат. Так за несколько лихорадочных недель, которые отделяли это первое объявление от начала поставок, родилась ныне знаменитая шина S100. Шина MITS на 100 линий вскоре стала фактически эталоном для рынка любительских ЭВМ, который в то время буквально взрывался от новых изготовителей, вскакивавших в автобус почти еженедельно. Разработчики назвали свою шину шиной Altair , но их конкуренты переименовали ее в шину S100 (за ее стандарт, 100 выводов) и последнее прозвище прилипло. К несчастью, эта шина в действительности не была полностью стандартизованной. В ней был выведен на переднюю панель дешифратор линии записи в память, но не все микро-ЭВМ имели переднюю панель. По поводу значения отдельных сигналов этой 1цины существовала путаница, приводившая к противоборству на ее линиях. Затем другие компании ввели свои собственные обозначения для различных неиспользованных линий (например, линия PHANTOM для вывода 67). Бывали случаи, когда изготовители снабжали свои платы ЦП входами для несуществующих линий синхронизации и т. д. В итоге никогда не было уверенности, что две SlOO-совместимые платы действительно смогут работать вместе внутри одной системы. Но, несмотря на все проблемы, которые тогда возникали при работе с шиной S100, многие изготовители и отдельные лИца создавали на ее основе относительно мощные и недорогие ЭВМ. В такой ситуации стоило затратить усилия, чтобы унорящочить порожденные шиной S100 проблемы. И вот комитет заинтересованных иненой выработал (с одобрения ИИЭР *) стандарт, который включал наименования и > Непереводимая игра слов. В аиглийск,ом языке шина и автобус обозначаются одним слово bus .- Прим. перев. 2> Институт инженеров по электротехнике и - радиоэлектронике (Ijisiilute of Electrical and Electronics Engineers, 1ЕЕЕ)*- Прима nepee.f функции сигналов и технические условия на синхронизацию. Этот новый стандарт узаконил шину S100. Изготовители теперь могут разрабатывать свои ЦП и периферийные устройства в соответствии со стандартом, указывающим те требования К выпускаемым ими платам, удовлетворение которых гарантирует возможность их совместной работы с любыми другими стандартизованными платами. Сигналы и синхронизация шины S100. В табл. И.8 приведены назначения выводов для стандартизованной ИИЭР шины S100. Пять Таблица 11.3 Сигналы шины S100 Функция Вывод функция Вывод функция Вывод функция

Примечания: звечдочка обозначает открытые коллекторные линии и повышенное допустимое напряжение. Ац по Л^а необязательны, б) Линии вывода данных DOp-DO, используются для (а) вывода данных н (б) 16-битовых В/В-передач, если это установлено запросом SXTRQ и ответом SIXTN. В) Восемь линий векторного прерывания. Г) Линия разрешения со следя щей связью, коллектор открыт. 1 ... 20 21 22 23 24 25 26 ... 59 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |