|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Методы подавления шумов, помех электронных систем 1 ... 55 56 57 58 59 60 Гц (например, от 55 до 65 Гц). Эта частота не может в точности равняться 60 Гц по следующим причинам: а) звезды и Солнце двн-л<утся с неодинаковой скоростью, поэтому потребуется частота порядка 60,1643 Гц; б) проходя наклонно через атмосферу, звездный свет претерпевает изгиб; это преломление зависит от зенитного угла, и, следовательно, видимое движение будет происходить с несколько неравномерной скоростью; в) иногда может возникнуть желание взглянуть на Луну, планеты или кометы, которые движутся с разными скоростя.ми. Эта задача решается с помощью 5-значного дискретного умножителя частоты, который формирует на выходе и\шульсы с частотой следования /gn/10\ где п- пятизначное десятичное число, устанавли-вае,\юе на передней панели с помощью двоично-десятичных барабанных переключателей, Частота сигнала на выходе удшожнтеля будет лежать где-то в районе 600 кГц, поскольку / формируется генератором с кварцевой стабилизацией и равна в точности 1 МГц. На выходе умножителя частота делится на 10* с помощью четырех декадных счетчиков, причем последний счетчик выполнен в виде делителя на 5, а после него установлен делитель на 2, служащий для получения симметричных импульсов с частотой 60 Гц. Для стабилизации амплитуды выходной сигнал поступает на ограничитель, выполненный на стабилитроне, а затем с помощью 6-звенного НЧ-фильтра Баттерворта с fo=90 Гц преобразуется в хороший синусоидальный сигнал. (Можно считать, что фильтр вычищает из прямоугольного сигнала высшие гармонические составляющие, или обертоны ). Затем с помощью усилителя с перекомпенсацией , рассмотренного в разд. 3.33, вырабатывается пере-мег.ное напряжение 115 В. Выходной сигнал фильтра на экране осциллографа выглядит идеальным, поскольку 6-звенный фильтр Баттерворта позволяет в данной схеме снизить наибольшую гармонику до 1,5% от значения амплитуды основной частоты, что означает затухание более чем на 35 дБ. Заметим, что данный метод формирования синусоидальных колебаний удобен лишь в том случае, когда частота входного сигнала ограничена узким диапазоном. Входы управления ±10% позволяют изменять частоту выходного chhn соидального сигнала на 10% за счет установки коэффициента деления третьего делителя, равным 9 или 11. Эта ступень представляет собой делитель по модулю п, показанный на рпс. 8.70. 8.31. Клавиатура с буферной памятью типа первым вошел, первым вышел Схема, показанная на рнс. 8.73, служит для сопряжения буквенно-цифровой клавиатуры с прибором-потребителем данных (например, ЭВМ) и использует для этой цели 64-символьную память типа первым ) 60 Гц - стандартная частота сети в США.- Прим. перев. (три сосюяния: WEfl.J-L Сима-*- Готовность 3341 гот + 5 - 74LS3B7 3341 B-, /7s /75 0 /?з 4 5. /?о %/r клавиатура, оаботанлцая Выхосной Земля A5CU строб 1,0 кОм 100кОм 7 74LS00 Сброс -\% ТГ- П Т7гГ47мнФ Сброй 68 ,.7415193 7us193 HP +5 5082-4650/ г 3900м СИД Уза- ТПОПЧЕ-ниб75% МСИС817!0№) адемгя г/з СРА8Н Уот iAjJ 5 ./5 0,01 заполнения \0-1 мА 5к0м 4,7к0м±. установка -4- т I IN914 полной шкалы Рис. 8,73, Клавиатура с буферной памятью типа первым вошел, первым вышел . вошел, первым вышел (разд. 8.27). Большинство клавиатур кодирует символы в 8-разрядном двоичном коде, известном под названием ASCII (см. гл. 10 и II), и по готовности каждого символа вырабатывает на выходе стробирующий импульс. Хорошие клавиатуры имеют защиту от дребезга контактов и, как правило, используют 2-клавишное буфе-рирование . Последнее означает, что в случае, когда нажимается вторая клавиша, а первая еще не отпущена, клавиатура вырабатывает два выходных кода в правильной последовательности. В рассматриваемой схеме символы, сформированные в коде ASCII, последовательно загружаются в устройство 3341 (память первым вошел, первым вышел с объемом 64X4, наращиваемая до 64x8) с помощью импульсов ввода (ВВ), вырабатываемых клавиатурой. Если в памяти содержится информация, она вырабатывает на выходе готовности ВЫСОКИЙ уровень, который сообщает внешнему прибору о том, что последний может забрать очередную порцию данных (в гл. 10 будет показано, как такое сообщение передается в ЭВМ и что потом она с ним делает). Внешний прибор забирает символ, вырабатывая импульс следующий символ (СЛЕД. СИМВ), который по входу вывод (ВЫВ) выгружает очередной символ из памяти и одновременно отпирает шинные формирователи с тремя состояниями типа 74LS367. Для того чтобы схема могла следить за состоянием буферного накопителя, в ее состав включены реверсивный счетчик и ЦАП (последний подробно будет описан в следующей главе), который вырабатывает сигнал для измерителя процента заполнения . По каждому сигналу ввод (ВВ) счетчик получает положительное приращение, а по каждому сигналу вывод (ВЫВ) - отрицательное. Счетчики и память сбрасываются сигналом установки в нуль, который вырабатывается либо при нажатии кнопки сброса, либо при включении питания (после включения схемы на одном из входов И-НЕ с помощью конденсатора 47 мкФ в течение приблизительно 0,15 с поддерживается НИЗКИЙ уровень). В любом устройстве с последовательной логикой при включении питания желательно производить установку схемы, в противном случае в начальный момент вы получите чепуху, так как все триггеры встанут в произвольные состояния. Схема содержит также светодиодный индикатор, который сигнализирует о том, что буфер заполнен на 75%; он начинает светиться, когда число в счетчике достигнет 48. Синхронизатор для реверсивных счетчиков. Предыдущая схема имеет один маленький недостаток. Несмотря на то что вход и выход памяти типа первым вошел, первым вышел полностью асинхронны (т. е. данные вводятся и выводятся в случайные моменты времени, которые могут даже перекрываться, если данные подготовлены к выводу), счетчик 74LSI93 не будет правильно работать, если импульсы на входах + и - будут совпадать в момент тактирования. При длительности стробирующего импульса, равной 1 мкс, это будет происходить не чаще, чем один раз на 100 ООО нажатий клавиш. Однако, если вы все же хотите предотвратить такую возможность, то можете использовать схему синхронизатора, аналогичную показанной на рис. 8.74. Сигналы ввод (ВВ) и вывод (ВЫВ) могут перекрываться, однако импульсы на входах + и - будут разделены во времени за счет стробирования тактами противоположной фазы, которые формируются внутренним генератором с частотой 1 МГц. Принцип работы схемы должен быть понятен без пояснений. 50 НС вед

Одно- д вибратор А ВЫВчо МГц jumn

50 НС Одно-вибратор К счбтчииам 74LSI92 Рис 8.74 Синхронизатор для реверсивных счетчиков. Промышленностью выпускается ЗУ типа первым вошел, первым вышел в виде стандартной БИС 3341, выполненной по МОП-технологии и имеющей входы и выходы, совместимые с уровнями ТТЛ. Это свойство обычно присуще большим интегральным схемам, выполненным на МОП-структурах, поскольку они часто используются совместно со схемами ТТЛ. 8.32. Формирователь последовательности из импульсов Формирователь последовательности из п импульсов представляет собой небольшой контрольный прибор, имеющий весьма широкое применение. По входному сигналу запуска он вырабатывает на выходе пачку из п импульсов с заданной частотой следования, которая может иметь ряд дискретных значений. Схема формирователя показана на рис. 8.75. Интегральные схемы 40102 представляют собой 2-декадные вычитающие счетчики семейства КМОП, на которые поступают тактовые импульсы от несинхронизированного генератора типа 555. Счетчики могут блокироваться НИЗКИМ уровнем по входу асинхронной загрузки (A3) или ВЫСОКИМ уровнем по входу переноса (ВХ. ПЕР). При поступлении запускающего импульса триггер 1 включает счетчик, а триггер 2 синхронизирует начало счета по спаду тактового импульса. Импульсы будут проходить на выход вентиля И-НЕ 3 до j 100 кГц + I2B Частота спедозаний импульсов 1 кГц 10 bTi;

2 МОм 0,022 Г Двоично десятичные переключатели барабаииого типа ЕЕСО 1)7Б 02G 412- резистор!. СЗР 7 Л

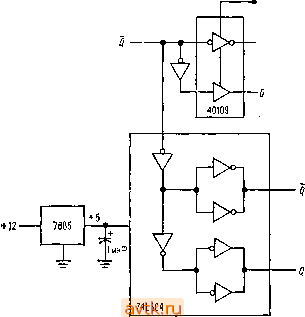

СЗР i i /? SPE A3 У (2 депаднои счетчик) ЫХ ПЕР СЗР все резисторь СЗР i > 0102 (2 декадный счетч.к! ff SPE ЛЗ V ч + 4- ЗЬХ PtP 17 Ом Запуск Д,  +Н/7 /? Taf ы 5,6 Ом HETppjs ЗТЕЛЬ L Последоват! иос'ь из п импулй Ручной ззпут (крэтиовремечныи контакт С К тг) 10107 Рис, 8.75, Лабораторный генератор последовательности из п ими\тьсов. тех пор, пока счетчик не досчитает до нуля. После этого оба триггера сбрасываются, и в счетчик от двоично-десятичных ключей параллельно вводится число п, счет блокируется, и схема подготавливается к следующему запуску. Заметим, что резисторы в данной схеме-подключены не к шине (/+, а к земле, следовательно, применяемые здесь двоично-десятичные ключи должны давать прямой, а не инверсный код. Отметим также, что вход ручного запуска должен иметь схему защиты от дребезга, поскольку он тактирует триггер. Для переключателя режимов, который просто разрешает формирование на выходе непрерывной последовательности импульсов, защита от дребезга не требуется. Разновидности выходных усилителей - формирователей. Выходной каскад типа 40107 представляет собой КМОП-вентиль И-НЕ с открытым стоком и повышенной нагрузочной способностью, который может управлять элементами ТТЛ или КМОП. Для того чтобы  Выходы с уровиями KMOfl Выходы с уровнями ТТЛ Рис. 8.76, выходной каскад обеспечивал НИЗКИЙ уровень требуемой величины, работающая от него схема должна иметь на входе нагрузочный резистор, подключенный к шине питания. Если вам нужно иметь чистые уровни и ТТЛ и КМОП без подключения дополнительной нагрузки к щине (/+ возбуждаемой схемы, то в этом случае следует применить схему, показанную на рис. 8.76. В ней выходы с уровнями КМОП фор- мируются с помощью преобразователя уровня 40109, который представляет собой кристалл КМОП с активными нагрузками, подключенными к дополнительному выводу питания, соединенному (в данной схеме) с шиной f/cc возбуждаемой схемы, значение которого может быть выше или ниже, чем t/cc У источника входных импульсов. Таким образом, на вход возбуждаемой схемы попадают чистые уровни КМОП при том же напряжении, на котором работает сама эта схема. К сожалению, элемент 40109 не обладает достаточной нагрузочной способностью для работы на входы ТТЛ, поэтому для формирования уровней ТТЛ используется сшестеренный инвертор 74LS04. Это означает, что, если вы не хотите запитывать элементы КМОП от того же напряжения +5 В, вам потребуется еще один источник питания. Что касается схемы ТТЛ, то здесь следует отметить два обстоятельства: а) для повышения нагрузочной способности инверторы можно соединять параллельно, если они расположены в одном кристалле; б) в большинстве маломощных вентилей ТТЛ-Шоттки на входе применяется диодная схема. Это позволяет использовать входные уровни до -flS В и, следовательно, непосредственно подключать йх к выходам КМОП, при условии что последние обладают достаточной нагрузочной способностью. Не пытайтесь, однако, сделать это с другими разновидностями схем семейства ТТЛ! Рассмотренная выходная схема иллюстрирует один из видов компромисса, с которым часто приходится иметь дело разработчикам. Она имеет улучшенные характеристики (активная нагрузка на выходах КМОП и уровни ТТЛ, обеспеченные без подключения к каким-либо внешним источникам), но требует наличия дополнительного источника напряжения, что не позволяет питать ее от одиночной 9-вольтовой батареи. В подобных ситуациях нужно решить, какой из факторов является наиболее важным. В некоторых случаях, правда, можно сразу убить всех зайцев, переходя к более сложной схеме на дискретных компонентах. Бесценную услугу здесь могут оказать хорошие знания схемотехники биполярных и полевых транзисторов. Этот вопрос будет подробно рассмотрен в гл. 9. ПАТОЛОГИИ В ЛОГИЧЕСКИХ СХЕМАХ Существуют интересные, а иногда просто забавные ловушки, которые подстерегают ничего не подозревающего разработчика цифровых схем. Некоторые из них, например логические гонки или ситуации заедания , могут возникать независимо от типа используемых логических схем. Другие, как, например, эффект тиристорного включения в кристаллах КМОП**, представляют собой генетические аномалии 1> Возникает вследствие наличия в КМОП-кристаллах четырехслойных структур р~п-р-п, образуемых стоками, подложками, диодами защиты и истоками, работакь Щих как плохие тиристоры при бросках питания,- Прим. ред. 8.33. Проблемы статических режимов Заедание . Очень легко попасть в ловушку, построив схему, имеющую мертвое состояние. Допустим, имеется какое-то устройство, содержащее ряд триггеров, которые в процессе работы проходят через заданные состояния. Кажется, что схема действует превосходно, но в один прекрасный момент она останавливается намертво. Единственный способ заставить ее опять работать - это выключить питание, а затем снова включить его. Такая ситуация возникла из-за того, что схема имела мертвое состояние (запрещенное состояние системы, которого не удалось избежать), в которое она и угодила под воздействием каких-то переходных помех по цепи питания. При разработке цифровых устройств необходимо выявлять подобные состояния и строить логику таким образом, чтобы схема могла . восстанавливаться авто.матически. Т Как минимум, должен быть преду- смотрен сигнал начальной установки (вырабатываемый от кнопки, при ут 1тл oicTCTBveT включении питания и т. д.), кото- оГъ - Р^ возвращал бы систему в нор- -°15 Т -f мальное состояние. При наличии tL 15 мкф t\ такого сигнала никаких других мер 23 в р^* может и не потребоваться (см. уп- ражнение 8.23). Начальная установка. Тот Рис. 8.77. Схема для формирования сиг- же вопрос возникает при определе-нала сброса при включении питания. НИИ состояния системы В Начальный люмект. В любо.м случае полезно иметь какой-либо сигнал, обеспечивающий начальную установку, иначе при включении пигапия в системе могут происходить непонятные вещи. Неплохая схе.ма начальной установки показана на рис. 8.77. При использовании КМОП необходимо последовательно со входом вентиля включить резистор, который позволяет избежать повреждения схемы при отключеппн питания, так как в противном случае электролитический конденсатор попытается запитать систему через защитный диод входного вентиля КМОП. Неплохой идеей является применение триггера Шмитта, благодаря которому снятие сигнала СБРОС происходит чисто . Си.мвол гистерезиса на рисунке означает, что на входе инвертора установлен триггер Ш.\штта, собранный, например, на ТТЛ 74LS14 (6 инверторов) либо КМОП 4093 (4 И-НЕ на 2 входа), либо 40106 (6 инверторов). ТОГО или иного семейства. В последующих разделах мы дадим обобщение нашего печального опыта и надеемся, что приведенные анекдоты помогут другим избежать тех же ошибок. 8.34. Проблемы при переключениях Логические гонки. Здесь скрывается множество коварных ловушек. Классический случай логических гонок был проиллюстрирован в разд. 8.19 на примере синхронизатора импульсов. В любом случае, когда вентили управляются сигналами от триггеров, необходимо убедиться в том, что в схеме не может возникнуть ситуация, когда к моменту тактирования триггера вентиль открывается, а затем по истечении задержки на триггере закрывается. Необходимо также, чтобы сигналы, возникающие на входах триггеров, не оказались задержанными по отношению к тактовым импульсам (еще одно преимущество синхронных систем!). В общем случае задерживайте такты, но не информацию. Проглядеть возможность возникновения логических гонок необычайно легко. Метастабильные состояния. Как уже отмечалось выше, триггер, а также любое тактируемое устройство может сбиться, если изменение сигналов на информационных входах произойдет менее чем за время tt. до возникновения тактового импульса. В худшем случае выход триггера будет буквально совершать колебания в окрестности логического порога в течение нескольких микросекунд (для сравнения: нормальная величина задержки распространения элементов ТТЛ составляет 20 не). Разработчики логических схем обычно не принимают это во внимание, однако подобная проблема может возникнуть в быстродействующих системах, когда требуется синхронизировать асинхронные сигналы. Такую ситуацию считают повинной во многих таинственных сбоях ЭВМ, однако мы смотрим на это предположение скептически. В этом случае требуется лишь установить цепочку синхронизаторов или детектор метастабильпых состояний , который будет сбрасывать (Триггер. Скос фронтов тактовых импульсов. Скос фронтов тактовых мн\-льсов оказывает большее влияние на схемы КМОП, чем на ТТЛ. 4015 В-разряднь1й рггипр срвйга Длиннь1й гровод ар=5мкс Заваленный фсонт тактового HMnvflbca - Рнс. 8.78, Временные сдвиги из-за завала тактовых импульсов, Паразитная емкость Подобная проблема возникает в том случае, когда для тактирования нескольких соединенных между собой устройств используется сигнал с большим временем нарастания (рис. 8.78). В рассматриваемом примере два регистра сдвига тактируются фронтом с большим временем нарастания. Это время обусловлено емкостной нагрузкой выхода КМОП который имеет относительно высокий импеданс (порядка 500 Ом при работе от источника +5 В). Проблема возникает вследствие того, что порог срабатывания у первого регистра может оказаться ниже, чем у второго, в результате чего его сдвиг произойдет раньше и последний бит первого регистра будет потерян. Дело еще осложняется тем, что значения пороговых напряжений для устройств на КМОП колеблются в очень широком диапазоне (фактически они могут принимать любое значение в пределах от 1/3 (/сс До 2/3 Ucc). В подобной ситуации самое лучшее - это располагать корпуса микросхем рядом, избегая большой емкостной нагрузки по тактовым входам. Укороченные импульсы. В разд. 8.28 при рассмотрении счетчика по модулю п мы отметили, что в том случае, когда счетчик должен сбрасываться собственным входным сигналом, необходимо ввести некоторую задержку для того, чтобы предотвратить появление укороченного импульса. То же самое относится и к импульсам записи в счетчики или регистры сдвига. Укороченные импульсы часто доставляют неприятности, приводя схему к работе на границе устойчивости и вызывая периодические сбои. При разработке схемы следует исходить из наихудшего Значения для задержки. 8.35. Прирожденные недостатки ТТЛ и КМОП Этот раздел мы разобьем на две части, в одной из которых рассмотрим проблемы, причиняющие неудобства разработчику, а в другой - по-настоящему ненормальное поведение логических элементов. Проблемы, причиняющие неудобства. ТТЛ. Не следует забывать о том, что при НИЗКОМ уровне входы ТТЛ действуют как источник тока. Это затрудняет применение в качестве элементов задержки 7?С-цепочек и аналогичных схем, поскольку они в этом случае должны иметь низкое сопротивление. При сопряжении линейных сигналов со входами ТТЛ вам, по-видимому, придется серьезно подумать и выработать какие-то идеи. Значение порога у элементов ТТЛ близко к уровню земли, вследствие чего все это логическое семейство в известной степени подвержено влиянию помех (более подробно см. гл. 9). Поскольку схемы ТТЛ являются быстродействующими, они воспринимают короткие пички по шине земли. Такие пички часто возникают при быстрой смене состояний на выходах, что еще более усугубляет проблему. Элементы ТТЛ предьявляют высокие требования к источнику питания: -f5 В ±5% при относительно высокой мощности рассеяния. Наличие токовых пичков, которые вырабатываются схемами с активной нагрузкой, как правило, требует обильного шунтирования источника питания, в идеальном случае - один конденсатор на каждый корпус ИМС. 1 ... 55 56 57 58 59 |

||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |