|

|

|

Разделы

Публикации

Популярные

Новые

|

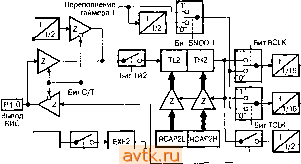

Главная » Классические однокристальные микроконтроллеры 1 2 3 4 5 6 7 8 ... 20 устанавливает в 1 бит EXF2. Оба бита - TF2 и EXF2 могут вызвать прерывание, если оно разрешено. Установка бита DCEN в 1 переводит таймер 2 в режим счета вверх и вниз, как показано на рис. 19, в. В этом режиме вывод Р1.1 управляет направлением счета. Единичный уровень на Р1.1 заставляет таймер 2 считать вверх. Таймер переполняется по достижении значения OFFFFH и устанавливает в 1 бит TF2. Это переполнение также вызовет перезагрузку 16-битного значения из RCAP2H и RCAP2L в регистры таймера ТН2 и TL2 соответственно. Нулевой уровень на Р 1.1 заставляет таймер 2 считать вниз. Теперь таймер антипереполняется , когда ТН2 и TL2 равны значениям, хранящимся в RCAP2H и RCAP2L. Антипереполнение устанавливает бит TF2 в 1 и вызывает перезагрузку OFFFFH в регистры таймера. Бит EXF2 переключается всякий раз при переполнении или антипереполнении таймера. Этот бит можно при необходимости использовать как 17-й бит таймера-счетчика. В этом режиме EXF2 не является флагом прерывания, и его установка в 1 не вызывает соответствующей подпрограммы. Генератор скорости передачи в бодах Таймер 2 превращается в генератор скорости передачи в бодах установкой в 1 битов TCLK и/или RCLK в T2CON (табл. 14). Отметим, что скорости в бодах для передачи и приема могут отличаться. Это достигается, например, при использовании таймера 2 для приема, а таймера 1 - для передачи (или наоборот). Установка RCLK и/или TCLK переводит таймер 2 в режим генератора скорости передачи в бодах, как показано на рис. 20. CLOCK CLOCK  БИс Детектор Бит Прерывание перепада tXLN таймера 2 БитТ20Е Режим генератора скорости передачи в бодах имеет сходство с режимом автоперезагрузки в том, что переполнение содержимого регистров таймера-счетчика TL2 и ТН2 вызывает перезагрузку регистров TL2 и ТН2 16-битным значением из регистров RCAP2H и RCAP2L, предварительно установленным программно. Скорости передачи в бодах в режимах 1 и 3 определяются следующим образом: Скорость в реж.1 и 3 = = (скорость переполнения таймера 2)/16 При этом таймер может работать как в режиме таймера, так и в режиме счетчика. В большинстве случаев выбирают режим таймера (С/ Т2 = 0). Обратим внимание читателей на одну особенность работы таймера-счетчика 2 при использовании его в качестве генератора скорости передачи в бодах. Обычно, как таймер, он инкрементирует свое содержимое в каждом машинном цикле с частотой, равной 1/12 частоты генератора). Однако, как генератор скорости передачи в бодах, он инкрементирует свое значение в 6 раз быстрее с частотой, равной 1/2 частоты генератора). Формула скорости передачи в бодах в зависимости от значений RCAP2L, RCAP2H выглядит следующим образом: Скорость в реж. 1 и 3 = - Частота генератора Рис. 20 4 [65536- (RCAP2H, RCAP2L)] где (RCAP2H, RCAP2L) - содержимое RCAP2H и RCAP2L, взятое как 16-битное целое число без знака. Отметим, что переполнение ТН2 не устанавливает TF2 и не вызывает прерывания. Кроме того, если EXEN2=1, то перепад из 1 в О в Р1.1 установит в 1 флаг EXF2, но не вызовет перезагрузки из RCAP2H, RCAP2L в ТН2, TL2. Таким образом, когда таймер 2 используется как генератор скорости передачи в бодах, вход Р1.1 может использоваться при необходимости как вход дополнительного внешнего прерывания. Следует отметить, что при работе таймера-счетчика 2 в таймер-ном режиме генератора скорости передачи в бодах нельзя пытаться считывать или записывать в ТН2 или TL2. В этом случае таймер инкрементируется 6 раз в течение каждого машинного цикла, и результаты чтения или записи будут неопределенными. Регистры RCAP2 можно читать, но нельзя в них записывать, т. к. запись может отменить ближайшую по времени перезагрузку и вызвать ошибки приема или передачи. Таймер должен быть отключен (TR2=0) перед об- ращением к регистрам таймера ТН2, TL2 или к регистрам RCAP2H, RCAP2L. Вывод программируемого сигнала меандра Вывод Р1.0 можно запрограммировать на использование в качестве генератора меандра (генератора прямоугольных импульсов с 50%-й скважностью). У микро-ЭВМ семейства 8052 этот вывод, помимо основной своей функции - функции ввода/вывода - может выполнять еще две дополнительные. Как упоминалось выше, он играет роль внешнего счетного входа для таймера-счетчика 2. Кроме того, он может быть источником прямоугольных импульсов с 50%-й скважностью и частотой в диапазоне от 61 Гц до 4 МГц при тактовой частоте генератора микро-ЭВМ 16 МГц. Для использования вывода Р1.0 в этом режиме бит С/Т2 (T2CON. 1) должен быть сброшен в О, а бит Т20Е (T2MOD.1) установлен в единицу. Бит TR2 (T2CON.2) запускает и останавливает таймер. Выходная частота генератора меандра зависит от частоты генератора микро-ЭВМ и значения, загруженного в регистры защелок (RCAP2H, TCAP2L) таймера 2, следующим образом: Частота генератора микро-ЭВМ Частота меандра на вых. Р1.0 = -р 65536- (RCAP2H, RCAP2L) где (RCAP2H,RCAP2L) - двухбайтовое содержимое этой регистровой пары, взятое как целое без знака. В описываемом режиме переполнение таймера-счетчика 2 не вызовет прерывания. Это похоже на режим использования таймера 2 как генератора скорости передачи в бодах. Можно использовать таймер 2 как генератор скорости передачи в бодах и как генератор меандра одновременно. Отметим, однако, что частоты передачи в бодах и генератора меандра нельзя определять независимо друг от друга, т. к. обе они используют RCAP2H и RCAP2L. Использование таймера 2 в режиме генератора меандра также иллюстрируется рис. 20. СИСТЕМА ПРЕРЫВАНИЙ Систему прерываний микро-ЭВМ семейства 8052 образуют описанные ранее пять прерываний микро-ЭВМ семейства 8051 и дополнительное прерывание от таймера 2 с вектором 2ВН. Кроме того, семейство 8052 дополнено еще одним регистром прерываний IPH, позволяющим увеличить количество возможных приоритетов для каждого из шести прерываний до четырех. Прерывание таймера 2 формируется логикой И битов TF2 и EXF2 в регистре T2CON. Оба этих флага должны сбрасываться программным путем, аппаратного сброса они не имеют. Подпрограмма прерывания должна самостоятельно определить, какой из этих флагов установлен, и сбросить его, вьшолнял после этого действия, предусмотренные в качестве реакции микро-ЭВМ на вызов прерывания. Структура прерываний 8052 приведена на рис. 21. IINTOl- Вывод БИС MUX г-П1>-1 I-1 1Бит1Т0 Детектор перепада 2 INT1- Вывод БИС 1бит|Т1 Детектор перепада 4 Бит EXF2

Рис. 21 Дополнительный регистр приоритетов прерываний IPH содержит 6 бит в соответствии с шестью источниками прерываний микро-ЭВМ (см. табл. 16). Каждый из этих битов является старшим битом приоритета соответствующего прерывания. Младший бит приоритета этого прерывания находится в регистре IP (см. в описании регистра в предыдущем разделе). Таким образом, уровень каж- Таблица 16 Дополнительный регистр приоритетов прерываний IPH

дого из прерываний определяется состоянием двух битов. Очевидно, что при помощи двух бит можно закодировать четыре различных числа - ООВ, 01В, 10В и 11В, что дает нам соответственно четыре уровня приоритета для каждого из источников О, 1, 2 и 3 , причем нулевой уровень соответствует низшему приоритету, а третий - высшему. УНИВЕРСАЛЬНЫЙ АСИНХРОННЫЙ ПРИЕМОПЕРЕДАТЧИК Приемопередатчик микро-ЭВМ семейства 8052 в целом идентичен приемопередатчику 8051 - те же четыре режима работы, различающиеся количеством передаваемых бит информации, скоростью передачи, условиями установки флагов прерывания RI или TI после приема или передачи байта информации. Другими словами, все, что было ранее сказано про приемопередатчик микро-ЭВМ 8051, справедливо и для 8052. Но последний имеет и ряд отличий от своих предшественников. Первое отличие приемопередатчика 8052 от 8051 мы уже описали - возможность работы приемопередатчика в режимах 1 и 3 не только от таймера 1, но и от таймера 2. Благодаря этой возможности разработчик при необходимости может использовать различающиеся между собой скорости приема и передачи без перенастройки таймеров. Следующим отличием приемопередатчика 8052 является наличие в нем устройства детектирования ошибок формата (Framing Error Detection). Это устройство позволяет последовательному порту проверять правильность стоп-битов в режимах 1, 2 или 3. Потеря стоп-бита может возникнуть, например, из-за шумов на линиях передачи или из-за одновременной передачи информации двумя процессорами мультимикропроцессорной системы. Если бит остановки потерян, устанавливается бит ошибки формата (FE). Этот бит может быть проверен программно после каждого приема для обнаружения ошибок связи. Будучи однажды установлен, бит ошибки формата может быть сброшен только программным путем. Если после установки бита ошибки формата он не был сброшен программно, а затем в результате следующего цикла обмена информацией получен байт данных с правильным стон-битом, сброса бита ошибки формата не произойдет. FE бит расположен в SCON и делит один адрес с SMO. Бит управления SMOD0 в регистре PCON (PCON.6) определяет, к какому биту обращается микропроцессор - к SMO или к FE. Если SMOD0 = О, то обращение к SMO. Если SMOD0 = 1 - к FE. И наконец, третьим отличием приемопередатчика 8052 от 8051 является автоматическое распознавание адреса. Автоматическое распоз- навание адреса уменьшает время, требуемое микро-ЭВМ на обслуживание последовательного порта. Поскольку в этом случае CPU не прерывается при получении адресного байта, отличного от своего собственного адреса, издержки CPU на сравнение адресов исключаются. Эта особенность микро-ЭВМ используется как правило в одном из 9-битовых режимов. При этом флаг прерывания от приемника (RI) устанавливается только тогда, когда полученный адресный байт совпадает с индивидуальным или с широковещательным адресом. Это отличие приемопередатчика 8052 можно использовать в мультимикропроцессорных системах следующим образом. Когда ведущий процессор хочет передать блок данных одному или нескольким подчиненным процессорам системы, он сначала посылает адресный байт, который идентифицирует нужный подчиненный компонент. Напомним, что в адресном байте 9-й бит установлен в 1, тогда как в байте данных 9-й бит установлен в 0. Во всех подчиненных процессорах их биты SM2 должны быть установлены в 1, т. е. они могут быть прерваны при приеме адресного байта. Способность автоматического распознавания адреса позволяет обеспечить прерывание только того подчиненного компонента, к которому адресуется ведущий процессор. В этом режиме сравнение адресов происходит аппаратно, а не программно. (В последовательном порте 80С51 адресный байт прерывает все подчиненные процессоры для сравнения адресов). Подчиненный процессор-получатель затем стирает свой бит SM2 и готовится к приему байтов данных. На остальные процессоры эти байты данных никак не действуют, и они продолжают выполнять свои программы до получения ими адресных байтов, соответствующих их заданным адресам. Так же, как в 9-битовых режимах 2 и 3, автоматическое распознавание адреса функционирует и в 8-битовом режиме 1. Однако в режиме 1 место 9-го бита данных занимает в RB8 стоп-бит. Если SM2 установлен, то флаг RI устанавливается только в случае, когда полученный байт соответсвует заданному или широковещательному адресам и сопровождается правильным стон-битом. Установка SM2 никак не проявляется в режиме 0. Ведущий процессор может избирательно связываться и с группами подчиненных процессоров. Адресация ко всем подчиненным сразу или к какой-либо группе из них возможна при использовании адресов, хранящихся в двух специальных функциональных регистрах SADDR и SADEN. Индивидуальные адреса подчиненных процессоров хранятся обычно в SADDR. SADEN - это масочный байт, определяющий незначащие биты для формирования заданного адреса. Эти незнача- щие биты придают гибкость определяемому пользователем протоколу для формирования адреса выбранного подчиненного процессора. Далее дан пример того, как можно использовать адреса, хранящиеся в SADDR и в SADEN для того, чтобы селективно адресовать разные подчиненные процессоры. Предположим, что в нашей системе имеется один ведущий процессор и два подчиненных, регистры SADDR и SADEN которых содержат следующую информацию: Подчиненный процессор 1; SADDR =1111 0001 В SADEM = 1111 1010 В Заданный адрес = 1111 ОХОХ Подчиненный процессор 2: SAODR = 1111 0011 В SADEN =1111 1001 В Заданный адрес =1111 0ХХ1 В Биты SADEN выбраны так, чтобы иметь возможность адресоваться к каждому подчиненному процессору отдельно. Заметим, что бит О - незначащий для заданного адреса подчиненного процессора 1, но бит О равен 1 для заданного адреса подчиненного процессора 2. Таким образом, для избирательной связи именно с первым подчиненным процессором ведущий процессор должен послать адрес, в котором бит О равен О (например, 1111 0000). Аналогично, бит 1 равен О для заданного адреса подчиненного процессора 1, но он же - незначащий для заданного адреса подчиненного процессора 2. Так что для связи именно с подчиненным процессором 2 должен использоваться бит 1, равный 1 (например, 1111 0111). Наконец, чтобы ведущий процессор связался с обоими подчиненными одновременно, в передаваемом адресе бит О должен быть равен 1, и бит 1 должен быть равен 0. Отметим, однако, что бит 2 - незначащий для обоих процессоров одновременно. Это позволяет двумя разными адресами выбирать оба подчиненных процессора (11110001 или 1111 0101). Если в систему добавился еще и третий подчиненный процессор, нужно потребовать, чтобы бит 2 его заданного адреса был равен 0. Тогда адрес 1111 0101 может использоваться для связи с процессорами 1 и 2, а адрес 11110001 - со всеми тремя процессорами одновременно. Для индивидуальной адресации тре- тьего процессора при .этом придется использовать третий и последующие биты адреса. Ведущий процессор может также связываться со всеми подчиненными одновременно с помощью широковещательного адреса. Он формируется логикой ИЛИ регистров SADDR и SADEN, при этом нули в SADEN по-прежнему определяют незначащие биты в адресном байте. Это также дает дополнительные возможности в выборе широковещательного адреса, но в большинстве применений широковещательным адресом выбирают OFFH. SADDR и SADEN расположены по адресам 0А9Н и 0В9Н соответственно. При сбросе регистры SADDR и SADEN устанавливаются в ООН.что определяет заданный и широковещательный адреса как ХХХХ ХХХХ (все биты неопределенные). Это гарантирует совместимость сверху вниз последовательного порта 8052 со своим предшественником 8051, не имеющим автоматического распознавания адреса. РЕЖИМ ПОНИЖЕННОГО ЭНЕРГОПОТРЕБЛЕНИЯ Микро-ЭВМ 8052 может выходить из режима пониженного энергопотребления как при аппаратном сбросе, так и при внешнем прерывании. Сброс переопределяет все регистры специальных функций, но не меняет содержимого внутреннего ОЗУ. Внешнее прерывание позволяет как регистрам (кроме бита PD в PCON), так и встроенному ОЗУ сохранять свои значения. Чтобы обеспечить правильный выход из этого режима, сброс или внешнее прерывание не должны подаваться прежде, чем Vcc восстановит свой нормальный рабочий уровень, и должны удерживаться достаточно долго, чтобы генератор перестартовал и стабилизировался (обычно менее 10 мс). При использовании для вывода из режима пониженного энергопотребления внешних прерываний ШГО или INT1 схема прерываний должна быть конфигурирована на срабатывание по уровню соответствующего сигнала. Удержание вывода при нулевом потенциале перестартует генератор, а перевод вывода в единичный уровень завершит выход. После выполнения команды RETI в подпрограмме обслуживания прерывания следующей будет выполняться та команда, которая идет после той, что перевела микро-ЭВМ в режим пониженного энергопотребления. ФЛАГ ОТКЛЮЧЕНИЯ ПИТАНИЯ Флаг отключения питания (РОЕ), расположенный в PCON.4, устанавливается аппаратно, когда Vss повышается от О до примерно 5 В. РОЕ может также быть установлен или стерт программно. Это позволяет пользователю различать сбросы холодного и теплого стартов. Сброс холодного старта совпадает с подачей на микро-ЭВМ напряжения питания. Сброс теплого старта происходит без отключения питания, например, при выходе из режима пониженного энергопотребления. Сразу же после сброса пользовательская программа может проверить состояние бита POF. POP = 1 означает холодный старт. Программа затем стирает POP и начинает свои задачи. POP = О сразу после сброса означает теплый старт. Для того, чтобы флаг POF удерживался в сброшенном состоянии, необходимо, чтобы напряжение питания не опускалось ниже 3 В. СПЕЦИАЛЬНЫЙ РЕЖИМ ЭМУЛЯЦИИ ONCE Данный режим позволяет выполнять тестирование и отладку систем, используюгцих микро-ЭВМ семейства 8052 без удаления последних из платы. Для активизации режима эмуляции необходимо выполнить следующую последовательность действий: при высоких логических уровнях на RST и PSEN подать уровень логического О на вывод ALE; удержать ALE в логического О при деактивации сигнала сброса на RST (подаче на RST уровня логического 0), после чего перестать удерживать ALE в состоянии логического 0. Во время нахождения микросхемы в режиме эмуляции выводы порта РО переходят в высокоимпедансное состояние, а выводы портов Р1-РЗ и выводы ALE, PSEN находятся в состоянии 1, которое обеспечивается с помощью внутренних высокоомных резисторов. Тракт генератора остается активным. В то время, когда микросхема находится в режиме эмуляции, для управления системой можно использовать внешний эмулятор или тестовый процессор. Нормальная работа схемы возобновляется после подачи нормального сигнала сброса на вход RST. ЗАЩИТА ВНУТРЕННЕЙ ПАМЯТИ ПРОГРАММ Микросхемы семейства 8052 содержат два механизма защиты внутренней памяти программ от несанкционированного доступа извне: проверку зашифрованного содержимого памяти программ и биты защиты памяти программ. Шифровальная таблица Микро-ЭВМ семейства 8052 имеют 64-байтную шифровальную таблицу, располагающуюся во внутреннем ПЗУ и программируемую пользователем или предприятием-изготовителем. Эта таблица (или область памяти) может использоваться для шифрования байтов внут- ренней памяти программ, выбираемых внешними средствами из ПЗУ во время проверки,его содержимого. Всякий раз, когда в режиме проверки адресуется байт внутреннего ПЗУ, 6 бит адреса используется для адресации шифровальной таблицы. Появляющийся на внешних выводах микросхемы байт является результатом выполнении операции ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ над байтом, выбранным из ПЗУ программ, и байтом, выбранным из шифровальной таблицы. Зная содержимое шифровальной таблицы, можно выполнить дешифрацию и получить истинное содержимое внутренней памяти программ. Незапрограммированные байты шифровальной таблицы содержат OFFH. Таким образом, если шифровальную таблицу оставить незапрограммированной, то в режиме проверки внутреннего ПЗУ будет считываться истинное значение его содержимого. Заметим, что незапрограммированные байты ПЗУ внутренней памяти программ также содержат OFFH. Необходимо иметь ввиду следующее обстоятельство. Если байт программной памяти содержит OFFH, то результатом операции ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ над ним и байтом шифровальной таблицы даст в результате значение байта шифровальной таблицы (аналогично тому, что такая операция над байтом ПЗУ и байтом таблицы, содержащим OFFH, даст значение байта из ПЗУ). Следовательно, если пользователь оставит незапрограммированным большой фрагмент памяти программ (хотя бы в 2...3 раза больший объема шифровальной таблицы), то определить ее содержимое становится несложно - повторяющийся несколько раз фрагмент из 64 байт и есть искомое содержимое. Поэтому незанятые пользовательской программой байты ПЗУ должны заполняться какой-либо информацией. Некоторые из типов микро-ЭВМ семейства 8051, выпускаемые фирмами Intel, AMD (8751ВН, 8752ВН), а также отечественные микро-ЭВМ КМ1830ВЕ751 и КМ1830ВЕ753 также содержат шифровальную таблицу, но объем ее ограничен 32 байтами. Микро-ЭВМ 87С51 последних модификаций содержит шифровальную таблицу объемом 64 байта. Более подробно об этом смотрите в описании на конкретную микро-ЭВМ. Биты защиты памяти программ Кодирование шифровальной таблицы, хотя и создает проблемы для нелегального копирования ПЗУ защищенной микро-ЭВМ, тем не менее не в состоянии сделать содержимое ПЗУ абсолютно недоступным. Для разработчиков микро-ЭВМ оказалась неприятным сюрпризом возможность считать информацию из защищенного внутреннего ПЗУ путем выполнения программы из внешнего ПЗУ, содержащей команды чтения байта ПЗУ (MOVC) с последующим выводом содержимого через, например, порт 1. С целью предотвращения подобных способов нелегального копирования система защиты памяти программ дополнилась еще одной ступенью. Она состоит в том, что кроме шифровальной таблицы микро-ЭВМ семейства 8052 содержат на кристалле один, два или три (в зависимости от модификации) бита защиты внутреннего ПЗУ, каждый из которых может быть запрограммирован (3) или оставлен незапрограммированным (Н) для получения следующих дополнительных свойств: Таблица 17 Биты защиты внутреннего ПЗУ

Если бит 1 запрограммирован, логический уровень на выводе ЕА опрашивается и фиксируется во внутренней защелке во время сброса. Если питание микросхемы включается без формирования сигнала сброса, запоминается случайное значение и сохраняется до активизации сигнала сброса. Для правильной работы микросхемы необходимо, чтобы значение логического уровня на выводе ЕА совпадало с состоянием защелки. ПРОГРАММИРОВАНИЕ МИКРО-ЭВМ СЕМЕЙСТВА 8052 Микросхемы семейства 8052 программируются с помощью специального алгоритма ( Алгоритм программирования укороченными импульсами ), отличающегося от более ранних модификаций величиной программирующего напряжения U, а также длительностью и количеством программирующих импульсов на выводе ALE/ PROG. В табл. 18 показаны логические уровни на выводах микросхем при программировании памяти программ, шифровальной таблицы II бит защиты памйти. Таблица 18 Режимы программирования УФ ПЗУ 87С52

Примечания. 1 1 - высокий логический уровень 2. О - низкий логический уровень 3. и = 12,75 В ±0,25 В 4. Ucc = 5 В + 10 % во время программирования и проверки Ток программирования от источника U не превышает 50 мА На вывод ALE/PROG подаются 25 программирующих импульсов, в то время как U удерживается на уровне 12,75 ±0,25 В. Каждый программирующий импульс подается низким логическим уровнем в течение 100 ± 10 мкс и высоким логическим уровнем - как минимум 10 мкс. Программирование и верификация памяти программ осуществляется, как видно из табл. 18, аналогично 8751, за исключением величины и и структуры сигнала на входе ALE/ PROG . Для программирования шифровальной таблицы используется тот же алгоритм, что и для программирования УФ-ПЗУ программ, но выводы микросхемы должны находиться в состояниях, приведенных в табл. 18 для режима Программирование шифровальной таблицы . При этом шифровальная таблица расположена в адресном пространстве от О до 3FH (О соответствует 1FH для 32-байтной версии). Не следует забывать, что после того, как шифровальная таблица запрограммирована, в режиме проверки из микросхемы будут счи-тываться только зашифрованные данные. Для программирования битов защиты памяти программ используется тот же алгоритм, что и для программирования УФ ПЗУ программ и ячеек шифровальной таблицы, но выводы микросхемы дол-; жны находиться в состояниях, приведенных в табл. 18 для режимов Программирование Бита п защиты памяти программ . После того, как один из бит защиты памяти программ запрограммирован, дальнейшее программирование внутренней памяти программ и шифровальной таблицы становится невозможным. Однако при этом другой бит защиты памяти может быть запрограммирован. Необходимо отметить, что вход ЕАА'рр очень чувствителен к превышениям максимально допустимого напряжения программирования, равного 13 В. Даже иголки ыше указанного уровня могут привести к необратимому отказу микросхем. Приложение 3 МИКРОКОНТРОЛЛЕРЫ ГРУПП 51 FX, 51GB И СЕМЕЙСТВА MCS251 ФИРМЫ INTEL МИКРОКОНТРОЛЛЕРЫ ГРУПП 8XC51FX, 8XL51FX в Приложении 2 мы подробно рассмотрели однокристальные микро-ЭВМ семейств MCS-51, MCS-52 фирмы Intel. Однако жизнь не стоит на месте, и разработчики Intel предложили нам более совершенные изделия, ставшие доступными отечественным радиолюбителям и профессионалам благодаря снятию различных ограничений и снижению цен на эти изделия до уровня 10...20 долларов за штуку. Ниже автор предлагает читателям поближе познакомиться с микроконтроллерами групп 8xC51Fx, 8xL51Fx все той же фирмы Intel. Микроконтроллеры упомянутых групп принадлежат к широко распространенному семейству MCS-51. Они являются одними из наиболее совершенных изделий этого семейства и обладают широкими функциональными возможностями. Автор предполагает, что читатели знакомы с микроконтроллерами 8x51х, 8хС51х, 8хС52х, являющимися предшественниками рассматриваемых микроконтроллеров, поэтому здесь описываются только отличия контроллеров 8xC51Fx, 8xL51Fx от своих предшественников. К группе 8xC51Fx относятся микроконтроллеры 80C51FA, 83C51FA, 87C51FA, 83C51FB, 87C51FB, 83C51FC, 87C51FC. В группу 8xL51Fx входят 80L51FA, 83L51FA, 87L51FA, 83L51FB, 87L51FB, 83L51FC, 87L51FC. Обе группы полностью совместимы архитектурно и по расположению выводов с базовой моделью MCS51 и имеют следующие отличия от нее: объем внутреннего ПЗУ - 8, 16 и 32 кбайт; объем внутреннего ОЗУ - 256 байт; три 16-битовых таймера/счетчика; . программируемый частотный вывод; таймер/счетчик с возможностью прямого и обратного счета; семь векторов прерываний, 4-уровневая структура прерываний; дуплексный программируемый последовательный порт, поддерживающий автоматическое распознавание адреса и аппаратное определение ошибки типа потеря стоп-бита ; режим ONCE - эмуляция без выпаивания кристалла; улучшенный алгоритм программирования быстрыми импульсами ; трехуровневая система защиты внутреннего ПЗУ; два режима уменьшенного энергопотребления (Idle и Power Down); CHMOS-технология, увеличенная тактовая частота (до 16...24 МГц); 3-вольтовое питание для микроконтроллеров группы 8xL5 IFx; наличие массива программируемых счетчиков, реализующих режимы: . сравнения/защелки; программируемого таймера; высокоскоростного выхода; широтно-импульсного модулятора; сторожевого таймера. Первые одиннадцать пунктов отличительных особенностей не являются принципиально новыми и реализованы в некоторых предыдущих микроконтроллерах - в частности, в семействе MCS-52. Новыми являются повышенная тактовая частота, 3-вольтовое питание и массив программируемых счетчиков. Рассмотрим эти отличия более подробно. ПОВЫШЕННАЯ ТАКТОВАЯ ЧАСТОТА Приведенная ниже табл. 1 дает информацию о наличии кристаллов с разными тактовыми частотами в группе 8хС51Ех (8xL51Fx не имеют подобного разнообразия в диапазоне рабочих частот, и все функционируют на частотах от 3,5 до 16 МГц). Кристаллы, промаркированные индексом 3 , работают на частоте 24 МГц только при использовании внутренних ПЗУ и ОЗУ. При использовании внешнего ПЗУ или Ov3y (или и того, и другого) предельная верхняя частота не должна превышать 20 МГц.

ПОНИЖЕННОЕ НАПРЯЖЕНИЕ ПИТАНИЯ Микроконтроллеры группы 8xL51Fx функционируют на тактовых частотах от 3,5 до 16 МГц при питающем напряжении от 2,7 до 3,6 В. Между собой кристаллы различаются также объемом внутреннего ПЗУ: у кристаллов с индексом А объем ПЗУ - 8 кбайт, с индексом В - 16 Кбайт, с индексом С - 32 кбайт. Аналогичное деление по объему ПЗУ и у микроконтроллеров группы 8хС51Ех. Микроконтроллеры 80C51FA и 80L51FA не имеют внутреннего ПЗУ. Кроме того, у 80C51FA, 80L51FA, 83C51FA и 83L51FA отсутствует режим программируемого частотного выхода у таймера/счетчика 2, система прерываний только двухуровневая, нет асинхронного сброса портов и нет системы защиты программной памяти. МАССИВ ПРОГРАММИРУЕМЫХ СЧЕТЧИКОВ Одним из наиболее существенных отличий микроконтроллеров семейства 8хС51Ех (8xL51Fx) является наличие массива программируемых счетчиков (РСА). РСА обеспечивает более широкие возможности, с меньшим отвлечением центрального процессорного устройства (ЦПУ), чем стандартный таймер-счетчик. К преимуществам РСА можно также отнести более простое его программирование и более высокую точность. К примеру, РСА может обеспечить лучшее временное разрешение, чем таймеры 0,1 или 2, т. к. счетчик РСА может работать втрое быстрее этих таймеров, РСА также может выполнять большое количество задач, выполнение которых с использованием таймеров требует дополнительных аппаратных затрат (например, определение фазового сдвига между импульсами или генерацию ШИМ-сигнала). РСА состоит из 16-битного таймера-счетчика и пяти 16-битных модулей сравнения-защелки (рис. 1). Таймер-счетчик РСА служит в качестве базового таймера для функционирования всех пяти модулей сравнения-защелки; ни один из других таймеров-счетчиков микрокон- 16 буп (каждый) 166иг i - Модуль 1 Модуль о Р1.3/СЕХ0 Р1.4/СЕХ1 Таймер/ i-1 I-1 счетчик -Ц Модуль 2 [ - [ Р1.5/СЕХ2 [ *! Модуль з| -> P1.6/CEX3 I Модуль 4 ) ->j PI .7/СЕХ4 Выводы ВИС троллера не может использоваться с этой целью. Вход таймера-счетчика РСА может быть запрограммирован на счет сигналов от следующих источников: выход делителя на 12 тактового генератора микроконтроллера; выход делителя на 4 тактового генератора микроконтроллера; сигнал переполнения таймера 0; внешний входной сигнал на выводе ЕС1 (Р1.2). Любой из модулей сравнения-защелки может быть запрограммирован для работы в следующих режимах: защелкивания по фронту и/или спаду импульса; программируемого таймера; высокоскоростного выхода; широтно-импульсного модулятора. Модуль 4 может быть также запрограммирован как сторожевой таймер (Watchdog Timer). При работе модуля сравнения-защелки в режиме защелки, программируемого таймера или высокоскоростного выхода модуль может сформировать сигнал прерывания. Сигналы от всех пяти модулей сравнения-защелки и сигнал переполнения таймера РСА разделяют один вектор прерывания. Иными словами, если прерывания разрешены, то и сигнал переполнения таймера РСА, и сигнал от любого из модулей вызывает одну и ту же подпрограмму прерываний, которая должна сама идентифицировать источник, вызвавший ее. Для работы с внешними устройствами таймер-счетчик РСА и модули сравнения-защелки используют выводы Р1 порта микро-ЭВМ. Эти выводы перечислены ниже (табл. 2). Если какой-либо вывод порта не используется при работе РСА или РСА, порт может использоваться стандартным образом. ТАЙМЕР-СЧЕТЧИК РСА РСА имеет 16-битный таймер-счетчик (рис. 2), состоящий из регистров СИ и CL (соответственно старший и младший байты). Эти регистры могут быть прочитаны и записаны в любое время. Чтение полного 16-битного значения таймера-счетчика РСА (далее для простоты таймера РСА) требует использования одного из РСА-моду-лей в режиме защелкивания. Рис. 1 Связь компонентов РСА и внешних выводов микро-ЭВМ

Fiakt/12- Ft акт/4 - Переполнение таймера О [есП Вывод БИС CPS1 CPSO 00 1 О К модулям 0...4 РСА CiDL. Режим IDLE процессора СН ! CL Прерывание Управление Рис. 2 Как отмечалось выше, пользователь может выбрать четыре варианта входных сигналов таймера РСА. 1. Частота тактового генератора, деленная на 12. При этом таймер РСА инкрементируется один раз в каждом махпинном цикле. Если тактовая частота равна 16 МГц, таймер инкрементируется каждые 750 не; 2. Частота тактового генератора, деленная на 4. Таймер РСА инкрементируется трижды в каждом машинном цикле, т. е. каждые 250 не при тактовой частоте генератора 16 МГц; 3. Переполнение таймера/счетчика О (Т/СО). Таймер РСА инкрементируется каждый раз, когда происходит переполнение Т /СО. Этот режим дает возможность программно задавать частоту входного сигнала таймера РСА; 4. Входной сигнал. Таймер РСА инкрементируется с переходом из 1 в О на выходе ECI (вывод Р1.2 микроконтроллера). Максимально допустимая частота сигнала на этом входе - частота тактового генератора, деленного на 8. Выбор входного сигнала осуществляется битами CPSO и CPS1 в регистре CMOD. В этом регистре также находится бит ECF, который разрешает прерывание при переполнении таймера РСА. Кроме того, Регистр режима счетчика РСА CMOD CIDL WDTE Позиция CMOD.7 CMOD.6 CPS1 CPSO CMOD.5 Имя и назначение Установка этого бита в 1 прекращает счет таймера РСА i- режиме Idle. При нулевом значении CIDL счет в режиме Idle не прекращается CMOD.4 CMOD.3 CMOD.2 CM0D.1 CMOD.O Бит управления сторожевым таймером. Установка его в 1 разрешает функционирование сторожевого таймера установка в О - запрещает Зарезервировано для дальнейшего использования Зарезервировано для дальнейшего использован1ля Заоеяеппмпппяип ппа п^г --- --!--,------цлш.пщсш ни1си;гьицаНИЯ Зарезервировано для дальнейшего исполь155; ЬыРор источника тактирования РСА. старший бит ВыбпП UnrnuUMl/o т-члт-... ------г^А -~--rrZ- выбор источника тактирования РСА. младший вы Бит ПЯ.ЧПР1Г1Саи1ла ппагм <п-1 ... ZZ - ~-~- Адрес регистра CMOD ~----I- ...г.. у .#л, iviJia/цщии иит Бит разрешения прерывания по переполнению таймера-счетчика РСА7. При ECF=1 разрешена установка бита CF регистра CCON, при ECF=0 - запрещена - 0D9H, значение по сбросу - ООхххОООЬ ~ установка в 1 бита CIDL дает возможность выключать таймер РСА в режиме Idle, что дает снижение энергопотребления в упомянутом режиме на 30 %. В табл. 3 приводятся имена и назначения битов регистра CMOD. Еще 2 бита, относящихся к таймеру-счетчику РСА, находятся в регистре CCON (описание регистра приведено в табл. 4). Бит СЕ устанавливается аппаратно при переполнении таймера-счетчика. Ус- Таблица 4 Регистр управления РСА CCON Позиция Имя и назначение CC0N.7 CC0N.6 CCF4 CCF3 CCF2 CCF1 CCFO Флаг переполнения счетчика РСА. Устанавливается- аппаратно и вызывает прерывание при ECF=1. Может быть установлен также и программно. Сброс только программным CCON.5 CC0N.4 CC0N.3 CCON.2 CC0N.1 CCON.0 Бит управления включением счетчика РСА. Установка его в 1 разрешает функционирование счетчика, установка в О - запрещает Зарезервировано для дальнейшего использования fbnor nnQK.. .r,. . .-ГТ----- -- f~ pricKimciu HUNUJ 1ЬЗОВаНИЯ прерывания модуля 4 РСА. Устанавливается аппаратно по равенству и фиксации значения. Очишается прпгпя.м.и^ Флаг прерывания модуля 3 РСА - Флаг прерывания модуля 2 РСА Флаг прерывания модуля 1 РСА -г---------- . Флаг прерывания модуля О РСА втт^ИтШлор - 0D8H. 3i;iii;;ij?t65537m тановка или сброс бита CR соответственно устанавливает или выключает счетчик. , МОДУЛИ СРАВНЕНИЯ-ЗАЩЕЛКИ Каждый из пяти модулей сравнения-защелки может функционировать в шести различных режимах: 16-битовый регистр-защелка с управлением по фронту импульса; 16-битовый регистр-защелка с управлением по спаду импульса; 16-битовый регистр-защелка с управлением как по фронту, так и по спаду импульса; .16-битовый программный таймер; 16-битный высокоскоростной выход; 8-битовый широтно-импульсный модулятор (ШИМ). Дополнительно модуль 4 может использоваться как строжевой таймер. Каждый модуль может быть запрограммирован на вьшол-нение любой из функций независимо от остальных. Каждый из модулей имеет регистр ССАРМп(п=0...4), с помощью которого осуществляется выбор режима его функционирования. Бит ЕССЕп в этом регистре разрешает прерывание от модуля РСА, если его флаг прерывания (ССЕп) был установлен. Эти флаги (CCF0-CCF4) находятся в регистре CCON и устанавливаются при описанных ниже условиях функционирования модуля в режиме защелки, программируемого таймера или режиме высокоскоростного выхода. Таблица 5 Регистр модуля сравнения-защелки п ССАРМп

1 2 3 4 5 6 7 8 ... 20 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |