|

|

|

Разделы

Публикации

Популярные

Новые

|

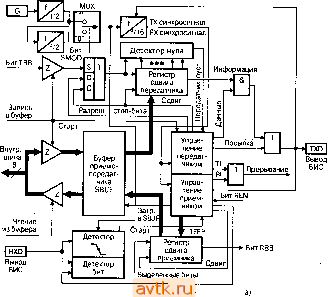

Главная » Классические однокристальные микроконтроллеры 1 2 3 4 5 6 7 ... 20 Если значение, принятое в первом такте, не равно О, то блок управления приемом вновь возвращается к поиску переходов из 1 в 0. Этот механизм обеспечивает подавление ложных (сбойных) старт-бит. Истинный старт-бит сдвигается в регистре приемника, и продолжается прием остальных бит посылки. Блок управления приемом сформирует сигнал Загрузка буфера , установит RB8 и флаг RI только в том случае, если в последнем такте сдвига выполняются два условия: бит RI=0 и либо SM2=0, либо принятый стоп-бит равен 1. Если хотя бы одно из этих двух условий не выполняется, то принятая последовательность бит теряется. В это время вне зависимости от того, выполняются указанные условия или нет, блок управления приемником вновь начинает отыскивать переход из 1 в О на входе RXD. В режимах 2 и 3 через вывод TXD приемопередатчик передает или с вывода RXD принимает 11 бит: старт-бит (0), 8 бит данных, программируемый девятый бит и стоп-бит (1). На временных диаграммах (рис. 13) показана работа приемопередатчика при передаче и приеме данных в режимах 2 и 3. Как видно из них, в этих режимах прием данных ничем не отличается от приема в режиме 1 за исключением того, что в бит RB8 в этих режимах заносится не стоп-бит, а девятый бит данных. Естественно, это никак не изменяет временные диаграммы в режимах 2 и 3 в сравнении с режимом 1. Необходимо также отметить, что несколько изменяются условия окончания цикла приема: блок управления приемником сформирует управляющий сигнал Загрузка буфера , загрузит RB8 и установит флаг RI только в том случае, если в последнем такте сдвига выполняются два условия: бит RI=0 и либо SM2=0, либо значение принятого девятого бита данных равно 1. При передаче данных в режимах 2 и 3 отличие от режима 1 состоит в том, что передаются не 8, а 9 бит данных, и вследствие этого цикл передачи оказывается на 1 полный период работы счетчика-делителя на 16 длиннее. Кроме того, как отмечалось выше, скорость обмена в режиме 2, в отличие от режимов 1 и 3, фиксирована и равна 1/32 или 1/64 от величины f рез РАБОТА ПРИЕМОПЕРЕДАТЧИКА В МУЛЬТИМИКРОПРОЦЕССОРНЫХ СИСТЕМАХ Описание приемопередатчика микро-ЭВМ семейства 8051 будет неполным, если не упомянуть еще об одной возможности, предусмотренной разработчиками фирмы Intel. Речь идет о работе приемопередатчика в системах децентрализованного управления. Такие системы используются для управления и регулирования в топологически распределенных объектах (в прокатных станах, в подвижном составе железных дорог и метрополитена, в сборочных кон- Переброс  ТХ синхросигнал -Запись вSBUF Л п п а. Опрос входного сигнала Передача fl JL Л П П TS1P1 Данные Сдвиг. Л-n n JL fl JL Старт-бит ,- сигнал -RXD- Разреш стоп-бита j Пересброс Прием rSSiJl-n JLiJl JLJl J JL Jl Старт- бит вхоГо™ I1ШLJJ1IU1I1J1J1I1 J1I1ILJ сигнала Сдвиг П П П П П п п п п п г Рис. 13 вейерах и линиях гибких автоматизированных производств). При Этом возникает задача обмена информацией между множеством микроконтроллеров, объединенных в локальную вычислительно-управляющую сеть. Как правило, локальные сети на основе 8051 имеют магистральную архитектуру с раздельным моноканалом (коаксиальный кабель, витая пара, оптическое волокно), по которому осуществляется обмен информацией между микро-ЭВМ. В регистре специальных функций SCON микро-ЭВМ имеется управляющий бит SM2, который в режимах 2 и 3 приемопередатчика позволяет относительно простыми средствами реализовать межпроцессорный обмен информацией в локальных управляющих сетях. Механизм межпроцессорного обмена информацией через последовательный порт 8051 построен на том, что в режимах 2 и 3 программируемый девятый бит данных при приеме фиксируется в бите RB8. Приемопередатчик может быть запрогрзхммирован таким образом, что при по.лучении стоп-бита прерывание от приемника будет возможно только при условии КВ8=]. Это выполняется установкой управляющего бита SM2 в регистре SCON. Поясним процесс межпроцессорного обмена информацией на примере. Пусть ведущей микро-ЭВМ требуется передать блок данных некоторой (или нескольким) ведомым. С этой целью ведущая микро-ЭВМ в протокольном режиме гпироковещательной передачи всем ведомым выдает в моноканал байт-идентификатор абонента (код адреса микро-ЭВМ-получателя), который отличается от байтов данных только тем, что в его девятом бите содержится 1. Программа реализации протокола сетевого обмена информацией долл?на быть построена таким образом, чтобы при получении байта-идентификатора (RB8=1) во всех ведомых микро-ЭВМ произошли прерывания прикладных программ и вызов подпрограммы сравнения байта-идентификатора с кодом собственного сетевого адреса. Адресуемая микро-ЭВМ сбрасывает свой управляющий бит SM2 и готовится к приему блока данных. Остальные ведомые микро-ЭВМ, адрес которых не совпал с кодом байта-идентификатора, оставляют неизменным состояние SM2=1 и передают управление основной программе. При SM2=1 информационные байты, передаваемые по моноканалу и поступающие в приемопередатчик ведомых микро-ЭВМ, прерывания не вызывают, т. е. игнорируются. В режиме 1 приемопередатчиком автономной микро-ЭВМ управляющий бит SM2 используется для контроля истинности стоп-бита (при SM2=1 прерывание не произойдет до тех пор, пока не будет получено истинное (единичное) значение стоп-бита). В режиме О бит SM2 не используется и должен быть сброшен. ПОШАГОВЫЙ РЕЖИМ ОТЛАДКИ АППАРАТНЫХ СРЕДСТВ И ПРОГРАММ Отладка прикладной программы может оказаться наиболее сложной задачей разработчика. Относительно высокая стоимость аппа- ратных и программных отладчиков приводит к тому, что в распоряжении разработчика на этапе отладки имеется в наличии лишь метод внимательного всматривания . Особую ценность в этом случае приобретает возможность пошагового (покомандного) выполнения отлаживаемой программы. В отличие от микро-ЭВМ семейства 8048, у микро-ЭВМ семейства 8051 отсутствует вывод, подачей на который соответствующего сигнала можно перевести микро-ЭВМ в режим ожидания. Тем не менее, пошаговый режим выполнения программы может быть легко реализован. Структура прерываний 8051 позволяет реализовать пошаговый режим работы с очень незначительными программными доработками. Как ранее отмечено, запрос прерывания не будет обслужен до тех пор, пока не завершится обработка прерывания с приоритетом равного или более высокого уровня, и пока после команды возврата из подпрограммы обслуживания прерывания RETI не выполниться хотя бы одна какая-либо команда. Таким образом, однажды вызванная программа прерывания не может быть вызвана повторно, пока она не будет завершена. Реализовать это свойство микро-ЭВМ для организации пошагового режима выполнения программы можно следующим образом. Необходимо запрограммировать одно из внешних прерываний (скажем, INTO) на срабатывание по уровню входного сигнала. Программа обслуживания прерывания должна заканчиваться следующими командами: JMB P3.2J JB Р3.2,$ RETI ;ждать, пока INTO не станет единичным ;ждать, пока INTO не станет равным нулю ; вернуться из прерывания и выполнить ;хотя бы одну команду ; (символом $ обозначено текущее содер-;жимое счетчика команд) Теперь если на выводе INTO, являющемся также выводом Р3.2, установится нулевой уровень сигнала, процессор начнет выполнение программы обслуживания внешнего прерывания О и останется в ней до тех пор, пока на INTO не появится единичный уровень, а вслед за ним и нулевой. Затем он выполнит команду возврата RETI, вернется к прерваной программе, выполнит одну команду и немедленно вызовет программу обслуживания внешнего прерывания О для ожидания следующего положительного импульса на входе Р3.2. Таким образом, при каждом импульсе на входе Р3.2 микро-ЭВМ выполняет одну команду ана;шзируемой прикладной программы. СБРОС МИКРО-ЭВМ в отличие от микро-ЭВМ семейства 8048, сброс микро-ЭВМ семейства 8051 осуществляется единичным уровнем сигнала. Этот сигнал должен быть приложен к выводу RST. Сброс достигается удержанием вывода RST вверху в течение, по крайней мере, двух машинных циклов (24 периодов колебаний) при работающем генераторе. CPU отвечает выработкой внутреннего сброса, алгоритм которого описан ниже (см. рис. 14). сигнал - сброса ALE ] PSBJ-1 S5 I S6 I SI I S2 ! S3 I S4 i S5 I S6 ! Si I S2 I S3 I S4 i S5 I S6 i SI I S2 I S3 ! S4 i iiiiiiiiiiiimiiii- 1 г коп X адР- X КОП 11 периодов Колеб. кв. генератора Г X коп Х адр. X КОП X адр. Х кОгГХ адр/ 19 периодов Колеб. кв. генератора Рис. 14 Внешний сигнал сброса асинхронен в отношении внутренних сигналов микро-ЭВМ. Вывод RST опрашивается в течение состояния 5 фазы 2 каждого машинного цикла. Поскольку выводы портов сохраняют свое текущее состояние в течение 19 периодов колебаний после обнаружения единицы на выводе RST, длительность сигнала сброса должна быть большей 19 периодов колебаний после сигнала внешнего сброса. Пока вывод RST имеет единичный уровень, выводы ALE и PSEN превращаются во входы, и потенциал на них медленно ползет вверх. После возврата RST в нулевой уровень требуется от 1 до 2 машинных циклов, чтобы ALE и PSEN начали синхронизироваться. Поэтому другие устройства нежелательно синхронизировать этими сигналами, если предполагается использовать сигнал сброса. Подача на выводы ALE и PSEN сигнала нулевого уровня в момент сброса может перевести микро-ЭВМ в неопределенное состояние. Алгоритм внутреннего сброса записывает нули во все регистры специальных функций кроме регистров-защелок портов ввода/вывода, указателя стека и SBUF. В защелках портов при инициализации установлено 0FFH, в указателе стека - 07Н, а содержимое SBUF неопределено. В табл. 11 приведен список регистров специальных функций и их значений после прохождения сигнала сброса. Состояние регистров SFR после сброса

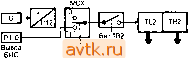

Примечание. X - значение бита неопределено Сброс не оказывает воздействия на состояние ячеек внутреннего ОЗУ микро-ЭВМ. Однако необходимо учитывать, что их состояние после включения питающего напряжения неопределено. СБРОС ПО ВКЛЮЧЕНИИ ПИТАНИЯ Если подача питающего напряжения не сопровождается достоверным сбросом ( т. е. удержанием единичного уровня на входе RST в течение 24 периодов резонатора), то микро-ЭВМ может начать выполнение программы до того, как в регистры специальных функций будут занесены значения, приведенные в табл. 11. При этом нельзя гарантировать корректность выполнения программы. Следовательно, микро-ЭВМ должна иметь цепи, обеспечивающие автоматическое формирование сигнала сброса при включении питания. Для микро-ЭВМ, выполненных по п-МОП технологии, при включении питания автоматическое формирование сигнала сброса может быть достигнуто соединением вывода RST с шиной питания через емкость 10 мкФ и с общим проводом через резистор 8,2 кОм . Для устройств к-МОП этот резистор не требуется, хотя его присутствие не повредит. Фактически, у к-МОП микро-ЭВМ этот резистор находится внутри, удерживая вход триггера Шмитта схемы сброса под потенциалом земли. Значение емкости для к-МОП версий микро-ЭВМ можно снизить до 1 мкФ. При включении питании подобная цепь удерживает высокий уровень на входе RST в течение времени, которое зависит от значения емкости и уровня, до которого она заряжена. Для гарантии достоверного сброса этот единичный уровень должен сохраняться дольше, чем генератор выработает 2 машинных цикла. Практика показывает, что при включении питания питаюгцее напряжение достигает своего номинального значения как правило в течение примерно 10 мс. Время запуска генератора зависит от его частоты. Для резонатора с частотой 10 МГц оно составляет обычно 1 мс, а для 1-МГц резонатора оно составит 10 мс. Следовательно, постоянная времени RC-цепи, соединенной с выводом RST, должна в несколько раз превосходить указанные временные интервалы и составлять 40...80 мс. В приведенной схеме резкое падение питающего напряжения вызывает мгновенное понижение напряжения на выводе RST ниже 0. Однако микро-ЭВМ снабжена внутренними ограничительными диодами, и эти броски напряжения не выводят ее из строя. Отметим также, что пока не запустится генератор микро-ЭВМ и не выполнится описанный выше алгоритм сброса, выводы портов РО-РЗ будут находиться в неопределенном состоянии. РЕЖИМЫ РАБОТЫ МИКРО-ЭВМ С ПОНИЖЕННЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ Во многих вариантах использования микро-ЭВМ энергопотребление является одним из основных параметров. В этих случаях целесообразно использовать к-МОП версии микро-ЭВМ. В этих версиях предусмотрены дополнительные возможности снижения потребления, отсутствующие в стандартных п-МОП изделиях. Ранее выпускались и п-МОП версии микро-ЭВМ, имевшие режимы работы с пониженным энергопотреблением. В настоящее время их выпуск почти повсеместно прекращен. Однако периодически они все-же будут попадать в руки радиолюбителей. Поэтому трудно гарантировать наличие или отсутствие этих режимов в тех или иных конкретных п-МОП изделиях. МАЛОПОТРЕБЛЯЮЩИЕ РЕЖИМЫ к-МОП ВЕРСИЙ Версии к-МОП имеют два режима с пониженным потреблением - режим холостого хода и режим выключенного напряжения питания. Иногда в литературе второй режим называют режимом пониженного энергопотребления. С точки зрения автора это вряд ли корректно, т. к. режим холостого хода тоже характеризуется понижен- 1 G К последовательному порту, таймерам-счетчикам, системе прерываний к CPU ным энергопотреблением в сравнении с обычным режимом работы микро-ЭВМ. Дословно второй режим, называемый в англоязычной литературе режимбм Power Down Mode , можно перевести так, как указано нами выше. Этот перевод корректнее отражает суть режима - в нем допустимо вообще отключить от микро-ЭВМ питающее напряжение, подаваемое на вход Vcc ( 40-й вывод корпуса микро-ЭВМ ). Для сохранения содержимого внутреннего ОЗУ его нужно запитать от резервного источника. При этом резервное питающее напряжение подается через вход RESET (вывод 9). На рис. 15 схематически показано, как реализуются эти режимы. В режиме холостого хода (IDL=1) генератор микро-ЭВМ работает, подавая вырабатываемые тактовые сигналы на схему прерываний, последовательный порт и на таймеры-счетчики. Все регистры сохраняют свое значение, на выводах всех портов удерживается то логическое состояние, которое было на них в момент перехода в режим холостого Рис. 15 хода. Однако синхросигнал генератора, синхронизирующий CPU, отключается. В режиме выключенного напряжения питания (PD=1) генератор останавливается. Прекращается тактирование не только CPU, но и последовательного порта, таймеров-счетчиков, схемы прерываний. Как и в режиме холостого хода, состояние регистров, резидентного ОЗУ и выводов портов остается неизменным. Режимы холостого хода и выключенного питания активируются при установке соответствующих битов в специальном функциональном регистре - регистре управления мощностью PCON. Адрес этого регистра - 87Н. Описание этого регистра было приведено в табл. 9. Отметим следующие особенности этого регистра. Если одновременно установлены в единицы биты IDL и PD, то бит PD имеет преимущество - микро-ЭВМ переходит в режим выключенного напряжения питания. Содержимое регистра PCON после сброса - (ОХХХОООО). В п-МОП версиях микро-ЭВМ регистр PCON содержит, как правило, только SMOD. Остальные 4 бита присутствуют только в к-МОП устройствах. Пользовательские программы никогда не должны заносить 1 в незанятые биты (PCON4...PCON6), т. к. они могут использоваться в последующих версиях микро-ЭВМ. Последнее распространяется на все регистры и все адреса в области регистров специальных функций, которые не заняты регистра- ми. Разработчики предполагают их использование в новых изделиях. Однако для достижения совместимости уже разработанного программного обеспечения с новыми изделиями дополнительные возможности последних будут включаться установкой в единицы битов в соответствующих регистрах. Поэтому пользовательская программа, устанавливающая в единицы неиспользуемые биты, будет нормально работать на микро-ЭВМ, имеющихся в наличии сегодня, но вовсе не обязательно будет работать на новых микро-ЭВМ, несмотря на их полную программную совместимость с семейством 8051. Режим холостого хода В режим холостого хода микро-ЭВМ переводится любой командой, устанавливающей в 1 бит PCON.0. Эта команда оказывается последней в цепочке выполняемых команд - в режиме холостого хода выполнение программы приостанавливается, т. к. на CPU перестает подаваться сигнал с тактового генератора. Однако содержимое внутреннего ОЗУ и регистров специальных функций остается неизменным, выводы портов удерживают значения, которые были на них до перехода в режим холостого хода. На таймеры-счетчики, приемопередатчик и схему прерывания продолжают поступать тактовые сигналы. На выводах ALE и PSEN устанавливаются сигналы единичного уровня. Состояние выводов портов зависит от типа ОЗУ, с которым микро-ЭВМ обменивалась информацией перед переходом в режим холостого хода. При работе с внутренним ОЗУ на выводах портов присутствуют данные из соответствующих SFR (естественно, если порт в режиме вывода информации). При работе с внешним ОЗУ выводы порта О переходят в высокоимпедансное состояние, а на выводах порта 2 сохраняется адресная информация. На выводах портов 1 и 3 присутствуют данные из SFR портов. Прекратить холостой ход возможно двумя способами. Вызов любого из прерываний приведет к аппаратному стиранию PCON.0, прекращающему холостой ход. Прерывание будет обслужено, и следующей после RETI выполняемой командой будет та команда, которая идет за командой, приведшей к переходу микро-ЭВМ в режим холостого хода. Флаги GEO и GF1 могут использоваться для индикации того, произошло ли прерывание во время нормальной работы или во время холостого хода. Например, команда, запускающая холостой ход, может также устанавливать один или оба флага. Когда холостой ход прекращен прерыванием, сервисная программа прерывания может проверять состояние флагов. Другой способ прекращения холостого хода - с помощью аппаратного сброса. Поскольку синхрогенератор продолжает рабо- хлть, аппаратный сброс должен поддерживаться в активном состоянии только в течение двух машинных циклов (24 периодов колебаний). Сигнал сброса стирает бит PCON.0. В этот момент CPU возобновляет выполнение программы с того места, где оно было остановлено; таким образом, следующая команда - та, что идет за командой, вызвавшей холостой ход. Как показано на рис. 14, перед началом отработки алгоритма внутреннего запуска могут иметь место 2 или 3 машинных цикла выполнения программы. Встроенное в микросхему устройство в это время препятствует доступу к внутреннему ОЗУ, но доступ к выводам порта не ограничен. Чтобы исключить возможность появления неопределенных выходных сигналов на выводах порта, команда, следующая за вызывающей холостой ход, не должна быть командой, записывающей информацию в SFR порта или во внешнее ОЗУ данных. Напомним, что после аппаратного сброса содержимое SFR переопределяется (см. табл. 11). Режим выключенного режима питания Команда, устанавливающая в 1 бит PC0N.1 переводит микро-v3BM в режим выключенного напряжения питания. В этом режиме генератор микро-ЭВМ останавливается. С остановкой синхро-генератора прекращает функционирование не только CPU, но и таймеры-счетчики, приемопередатчик, схема прерываний. При наличии основного или резервного источника питающего напряжения встроенное ОЗУ и регистры SFR сохраняют свое содержимое. Состояние портов не отличается от состояния при переходе в режим холостого хода (см. выше). Однако в отличие от режима холостого хода на выводах ALE и PSEN устанавливаются сигналы нулевого уровня. Единственный способ выйти из этого режима - аппаратный сброс. Он переопределяет содержимое всех SFR, как указано в табл. 11, но не меняет содержимого встроенного ОЗУ. В рассматриваемом режиме Vcc может снижаться вплоть до 2 В. Следует, однако, позаботиться, чтобы Vcc снижалось не раньше перехода в режим выключенного напряжения питания и возвращалось на свой нормальный рабочий уровень до выхода из этого режима. Сброс, возвращающий микро-ЭВМ в обычный режим, не должен подаваться раньше, чем Vcc достигнет своего нормального рабочего уровня, и должен поддерживаться в активном состоянии достаточно долго, чтобы генератор успел перестартовать и стабилизироваться (обычно не менее 10 мс). ВЕРСИИ СО СТИРАЕМЫМ УФ-ПЗУ Существует несколько различных версий микро-ЭВМ с УФ-ПЗУ, различающихся алгоритмами программирования и программирующими напряжениями. Как правило, п-МОП микро-ЭВМ программируются при напряжении программирования на входе Vpp от 21 до 25 В. При этом для записи каждого байта используется один 50-мил-лисекундный импульс. Общее время программирования составляет примерно 4 минуты. Большинство к-МОП версий микро-ЭВМ использует более быстрый алгоритм программирования Quick-Pulse . Эти устройства программируются при подаче на вход Vpp напряжения 12,75 В с использованием последовательности из 25 ШО-микросекундньгх: импульсов для записи одного байта программы. В результате общее время программирования составляет примерно 13 с. Подробно процедуры программирования и проверки каждого из устройств приведены в их технических условиях. Здесь мы рассмотрим только стандартный режим программирования п-МОП микросхем 50-миллисекундными импульсами. При программировании микро-ЭВМ должна работать на пониженной частоте (4...6 МГц) из-за необходимости мультиплексирования на внутренней шине адресной и кодовой информации. Схема подключения микро-ЭВМ к программатору приведена на рис. 16. Адрес ячейки ПЗУ, в которую должен быть загружен байт прикладной программы, подается на выводы порта 1 и Р2.0-Р2.3 порта 2. При этом загружаемый байт поступает в микро-ЭВМ через выводы порта 0. Выводы Р2.4...Р2.6 и PSEN должны быть заземлены, а на выводы Р2.7 и RESET необходимо подать уровень логической 1. На входе ЕА поддерживается уровень -1-5 В, но в момент загрузки байта он должен быть подключен к источнику напряжения с уровнем -Ь21 В. В это время уровень на входе ALE в течение не менее чем 50 мс должен быть нулевым. После этого напряжение на входе ЕА должно возвратиться к уровню -Ь5 В. Источник -Ь21 В должен быть хорошо стабилизирован, т. к. снижение напряжения программирования под нагрузкой приводит к сбою программирования, а превышение напряжения более чем на 1 В может привести к необратимому повреждению микросхемы. Бит защиты, будучи установлен, делает невозможным доступ к внутреннему ПЗУ микро-ЭВМ для любых попыток прочесть его со- А0...А7 вбит 4 бит -PI.7 Р2.0 -Р2.3 Р2.4 Р2.5 Р2,6 Р2.7 РО. -Р0.7 ЕА 21 8бит ° -1 г-+5 В -, +21 в L +5 В Рис. 16 держимое извне. Процедура записи бита защиты такая же, как и процедура занесения программы во внутреннее ПЗУ. Разница состоит в том, что на вывод Р2.6 должен быть подан уровень логической 1. Сигналы на выводах портов Р0,Р1 и Р2.0-Р2.3 при записи бита защиты могут быть произвольными. Первоначально разработчиками микро-ЭВМ семейства 8051 предполагалось, что установленный бит защиты молено сбросить только путем полного стирания информации из внутреннего ПЗУ под воздействием УФ-излучения. Однако техническому совершенству специалистов в области программного пиратства нет предела - некоторым из них удавалось стереть узконаправленным УФ-пучком только бит защиты, не повредив при этом информацию в ПЗУ. Подобные сообщения побудили разработчиков усложнить систему защиты информации в микро-ЭВМ, сделав ее трехступенчатой. Описание системы защиты информации в новых версиях микро-ЭВМ будет дано ниже. Если бит защиты не установлен, содержимое внутреннего ПЗУ может быть прочитано с целью проверки правильности загрузки прикладной программы. Подобная верификация может проводиться как по ходу программирования ПЗУ, так и после программирования. Схема подачи адресной информации не отличается от описанной для режима программирования ПЗУ, с той лишь разницей, что на вывод Р2.7 необходимо подавать нулевой уровень, используемый в качестве строб-сигнала чтения. Реакция ПЗУ микро-ЭВМ на свет Принято закрывать окно микро-ЭВМ непрозрачной наклейкой при использовании ее в реальных устройствах. Это необходимо не столько для того, чтобы защитить матрицу ПЗУ, сколько для того, чтобы защитить внутреннее ОЗУ и другие элементы внутренней структуры микро-ЭВМ. Попадание света на кремниевую подложку или на кристалл иногда приводит к сбоям в работе микро-ЭВМ вследствие ионизации кремния. Стирание содержимого внутреннего ПЗУ микро-ЭВМ осуществляется помещением ее под источник УФ-излучения с длиной волны менее 400 нм. Если кварцевая лампа имеет мощность 12 мВт на квадратный сантиметр, а расстояние между источником света и микро-ЭВМ 1...2 см, то выдержка 10...15 минут обеспечивает световую дозу, достаточную для надежного стирания информации из ПЗУ. Однако не стоит передерживать микро-ЭВМ под лучами УФтисточника - даже иолутора-двухкратное превышение указанной дозы иногда приводит к выходу микросхемы из строя. Так как в спектре солнечного излучения и люминисцентных ламп содержится излучение с длиной волны менее 400 нм, то пребывание микро-ЭВМ под воздействием этих источников света дольше установленного предела (около недели при солнечном освещении и около трех лет под люминисцентными лампами) может привести к искажению содержимого внутреннего ПЗУ. В этом случае также рекомендуется заклеивать входное окно микросхемы непрозрачным экраном. ВСТРОЕННЫЙ ТАКТОВЫЙ ГЕНЕРАТОР Встроенный тактовый генератор для п-МОП версий микро-ЭВМ представляет собой обычный инвертор, предназначенный для использования в качестве элемента с положительным реактивным сопротивлением в цепи обратной связи. Роль реактивного сопротивления играет кристалл кварца или керамический резонатор. Упрощенная схема тактового генератора п-МОП версии микро-ЭВМ приведена на рис. 17. Значения емкостей С1 и С2 существенной роли не играют. При использовании кварцевого резонатора рекомендуемые номиналы - 30 пФ. сигналов Ylpn использовании керамического резонатора значения емкостей рекомендуется увеличить до 47 пФ. Частотные характеристики емкостей и их температурный диапазон определяются требованиями к разрабатываемой системе. В ряде случаев разработчики используют внешний тактовый генератор, сигналами которого необходимо синхронизовать микро-ЭВМ. При этом внутренний генератор отключается. Для реализации этого режима вход XI микро-ЭВМ (вывод 19) необходимо заземлить, подав синхросигнал с внешнего генератора на вход Х2 (вывод 18). Для повышения помехоустойчивости вывод Х2 при этом рекомендуется 8751 Формирование внутренних -П|-- С1 Л.С2 Рис. 17 соединить с общим проводом через резистор номиналом 10...20 кОм. - & 87С51 cijHQ Формирование внутренних сигналов Рис. 18 ТАКТОВЫЕ ГЕНЕРАТОРЫ К-МОП ВЕРСИЙ Схема встроенного генератора к-МОП микро-ЭВМ показана на рис. 18. В целом он похож на генератор п-МОП микро-ЭВМ, но имеет ряд отличий от последнего. Первое отличие в том, что к-МОП микро-ЭВМ способны отключать свой генератор программным путем (записью 1 в бит PD регистра PCON). Другое отличие состоит в том, что сигнал внешнего синхрогенератора должен быть подан на вход XI ( вход Х2 не используется ), тогда как в версиях п-МОП - на Х2 при заземленном XI. Генератор можно использовать с теми же внешними компонентами, как в версиях п-МОП. Обычно, если элементом обратной связи является кристалл кварца, то С1 = С2 = 30 пФ, а если используется керамический резонатор - С1=С2 =47 пФ. Однокристальные микро-ЭВМ семейства 8052 ВВЕДЕНИЕ Создав удачную микро-ЭВМ 8051, разработчики не остановились на достигнутом и начали поиски вариантов ее усовершенствования. При этом им было необходимо не просто расширить функциональные возможности микро-ЭВМ и повысить ее производительность, но и выполнить ее программно-совместимой с семейством 8051. Последнее означает, что все программы, написанные для 8051, и все варианты ее аппаратного использования должны без каких-либо доработок выполняться на новой микро-ЭВМ. Отмеченные требования предопределили пути совершенствования рассматриваемого семейства. Этим требованиям удовлетворяет увеличение памяти программ на кристалле вплоть до 64 кбайт, введение дополнительных регистров специальных функций и новых режимов работы, повышение защищенности программ от нелегального копирования, использование линий порта 1 в альтернативных режимах (подобно линиям порта 3, как было описано ранее). Оказалось возможным расширить систему прерываний и сделать ее более гибкой. Возможно также создать специальные трехвольтовые малопотребляющие версии микро-ЭВМ, функционирующие при напряжении питания от 3 до 3,6 В, что делает их незаменимыми в аппаратуре с автономным питанием (литиевая батарея или три обычных 1-, 2-вольтовых аккумулятора). Желательно также расширить объем внутренней памяти данных, хотя последнее отнюдь не так просто реализовать, как вышеупомянутые доработки. В результате этих доработок появились микро-ЭВМ семейства 8052. Правда, это семейство вряд ли можно рассматривать как самостоятельное - для этих микро-ЭВМ справедливо абсолютно все, что ранее было сказано относительно 8051. Но в то же время эти микро-ЭВМ образуют самостоятельное подсемейство в семействе 8051, так как между собой они различаются лишь наличием или отсутствием внутренней памяти программ и объемом этой памяти, а их новые (в сравнении с 8051 ) функциональные возможности достаточно вели- ки. Рассмотрению отличий микро-ЭВМ семейства 8052 от 8051 посвящен настоящий раздел. СОСТАВ СЕМЕЙСТВА В состав рассматриваемого семейства входят микро-ЭВМ 80С52, 80С54, 80С58 с масочно программируемым ПЗУ объемом 8, 16 и 32 Кбайт соответственно, их УФ-стираемые версии 87С52, 87С54 и 87С58, а также микро-ЭВМ 80С32, не имеющая внутреннего ПЗУ. Между собой они различаются исполнением корпуса, диапазоном допустимых температур, предельно допустимой тактовой частотой и рядом других параметров, что отражается в буквенно-цифровой информации после обозначения типа микро-ЭВМ. Эту информацию можно получить в фирменных руководствах производителей микро-ЭВМ рассматриваемого семейства. Основными отличиями микро-ЭВМ семейства 8052 являются: встроенное ОЗУ объемом 256 байт; дополнительные специальные функциональные регистры; таймер 2, имеющий следующие режимы работы; режим защелки; таймер/счетчик, допускающий счет как на увеличение, так и на уменьшение; генератор скорости передачи в бодах. программируемый последовательный интерфейс с: детектированием ошибок передачи; автоматическим распознаванием адреса; 6 источников прерываний; расширенный режим снижения потребляемой мощности; флаг отключения питания; режим ONCE. Микро-ЭВМ 8052 используют стандартный набор команд 8051, ее выводы взаимно-однозначно соответствуют выводам микро-ЭВМ семейства 8051. Отличие заключается в том, что выводы Р1.0 и Р1.1 могут выполнять альтернативные функции помимо ввода/вывода информации. Вывод Р1.0 играет роль внешнего входа для счетчика таймера 2, а вывод Р1.1 управляет перезагрузкой/защелкиванием информации в регистры таймера 2. ВНУТРЕННЯЯ ПАМЯТЬ ДАННЫХ Микро-ЭВМ семейства 8052 имеют 256 байт внутреннего ОЗУ. Младшие 128 байт аналогичны внутреннему ОЗУ семейства 8051. Старшие 128 байт занимают адресное пространство, параллельное пространству специальных функциональных регистров. Это озна- чает, что они имеют те же адреса, что и регистры, но физически они являются независимыми от SFR и расположены в другой части кристалла микросхемы. При вьшолнении команды обращения к внутреннему ОЗУ с адресами выше 7FH CPU по режиму адресации, использованному в команде, узнает, к чему именно это обращение: к старшим 128 байтам ОЗУ или к пространству SFR. Команды с прямой адресацией обеспечивают доступ к пространству SFR. Например, команда MOV ОАОН, #data; (прямая адресация) обращается к SFR, расположенному по адресу ОАОН (т. е. к Р2). Команда с косвенной адресацией обращается к старшим 128 байтам ОЗУ, например MOV (S)RO, Sdata; (косвенная адресация), где R0 содержит ОАОН, обращается к байту с адресом ОАОН в пространстве старших 128 байт ОЗУ. Отметим, что работа стека организована с применением косвенной адресации (адрес используемой под стек ячейки памяти размещен в регистре SP), так что старшие 128 байт данных ОЗУ прекрасно подходят для размещения в них стека микро-ЭВМ. ПРОСТРАНСТВО СПЕЦИАЛЬНЫХ ФУНКЦИОНАЛЬНЫХ РЕГИСТРОВ Карта встроенной матрицы памяти, называемая пространством специальных функциональных регистров (SFR), дана в табл. 12. Отметим, что несмотря на ее более полное использование в сравнении с семейством 8051 по-прежнему не все адреса заняты реально существующими регистрами. Ячейки, соответствующие незанятым адресам, физически отсутствуют на кристалле микросхемы. Чтение при обращении к этим адресам возвращает случайные данные, запись в такие ячейки также даст неопределенный результат. Пользовательские программы не должны записывать единицы в эти незанятые позиции, т. к. они будут использованы в новых разработках. Разработчики микро-ЭВМ гарантируют, что нулевые значения этих битов всегда будут означать отключение вновь введенных функций. Последнее означает, что программы, рассчитанные на использование в микро-ЭВМ, не имеющих этих новых функций, будут корректно работать и в новых изделиях, если они не активируют упомянутые биты. В противном случае корректная работа старых программ в новых микро-ЭВМ не гарантируется. Как видно из табл. 12, она дополнилась рядом дополнительных регистров - регистрами второго таймера T2CON, T2MOD (в них содержатся биты управления и статуса таймера), RCAP2H и RCAP2L (регистры защелки/перезагрузки таймера), регистрами приемопередатчика SADDR и SADEN и дополнительным регистром системы Специальные функциональные регистры 8052 Регистр управления таймера-счетчика 2 T2CON

прерываний IPH. Ниже мы подробно опишем отличия в функционировании микро-ЭВМ семейства 8052 от 8051 и то, как при этом используются упомянутые регистры. ТАЙМЕР 2 Таймер 2 - это 16-битный таймер/счетчик, способный работать и как таймер, и как счетчик событий. Выбор производится битом С/Т2 в SFR T2CON (табл. 13). Таймер может работать в трех различных режимах - режиме защелки, режиме автоперезагрузки (при этом направление счета может быть как вверх, так и вниз, т. е. на увеличение или уменьшение содержимого TL2,TH2) и в режиме генератора скорости передачи в бодах. Режимы выбираются битами в T2CON, как показано в табл. 14. Таймер 2 состоит из двух 8-битных регистров, ТН2 и TL2. В режиме таймера его 16-разрядный регистр TL2, ТН2 инкрементируется в каждом машинном цикле. Так как каждый машинный цикл состоит из 12 периодов колебаний, скорость счета равна 1/12 частоты генератора. По сути дела в этом режиме происходит подсчет таймером выполненных машинных циклов. В режиме счетчика регистр инкрементируется в ответ на перепад из 1 в О на соответствующем контакте внешнего ввода Р1.0. В этом

Примечание. При сбросе все биты регистра T2C0N устанавливаются в О Таблица 14 Режимы работы таймера-счетчика 2

режиме внешний ввод анализируется в момент S5P2 каждого машинного цикла. Когда анализ показывает наличие единичного уровня в одном цикле и нулевого в следующем, содержимое счетчика инкрементируется. Новое значение счетчика появляется в регистре в момент S3P1 цикла, следующего за тем, в котором переход был обнаружен. Так как обнаружение этого перехода занимает 2 машинных цикла (24 периода колебаний), то максимальная скорость счета составляет 1/24 частоты генератора. Для гарантии того, что заданный уровень идентифицирован микро-ЭВМ перед тем, как он изменится, он должен удерживаться по крайней мере в течение 1-го полного машинного цикла. Режим защелки В режиме защелки есть два режима, выбираемых битом EXEN2 в T2C0N. Если EXEN2 = О, то таймер 2 - это 16-битный таймер или счетчик, при переполнении которого устанавливается бит TF2 в T2C0N. Этот бит затем может использоваться для вызова прерывания. Если EXEN2 = 1, то таймер 2 продолжает делать то же самое, но с тем дополнением, что перепад из 1 в О на внешнем вводе Р 1.1 вызывает защелкивание текущих значений ТН2 и TL2 в RCAP2H и RCAP2L соответственно. Кроме того, этот перепад вызывает установку в 1 бита EXF2 в T2CON. Бит EXF2, как и TF2, может вызвать прерывание. Режим защелки иллюстрирует рис. 19, а. Режим автоперезагрузки Если таймер 2 работает в режиме 16-битного таймера-счетчика с автоперезагрузкой, то он может быть настроен на счет вверх или вниз (увеличение или уменьптение содержимого регистров TL2, ТН2). Этот режим вызывается установкой в 1 бита DCEN (Down Counter Enable), расположенного в T2MOD (см. табл. 15). При сбросе бит DCEN устанавливается в О, так что таймер 2 по умолчанию считает вверх. Когда DCEN установлен, таймер 2 может считать вверх или вниз в зависимости от значения на выводе Р1.1. На рис. 19, б показан таймер 2, считающий на увеличение при DCEN 0. В этом режиме имеются два подрежима, выбираемых битом EXEN2 в T2CON. Если EXEN2 = О, то таймер 2 считает вверх до OFFFFH и затем устанавливает в 1 бит переполнения TF2. Переполнение вызывает также перезагрузку регистров таймера 16-битным значением в RCAP2H и RCAP2L. Значения RCAP2H и RCAP2L предварительно должны быть установлены программно. Если EXEN2 =1, 16-битная перезагрузка может срабатывать как от переполнения, так и от перепада из 1 в О на внешнем входе Р1.1. Этот перепад также Рис. 19  Переполнение Бит С/Т Вывод БИС Двгеиор Бит перепада tXEN2 RCAP2lrCAP2H

iPi.Oh Вывод БИС Бит С/Т БитТР2 Л Г Rumnn I......I-I < i .Л Бис Детектор Бит перепада илиг).; rCAP2l[rCAP2h Вывод БИС offh offh Бит с/Т 17-й бит Направление счета 1 - вверх О - вниз Вывод БИС rCAP2lrCAP2h[ Таблица 15 Регистр режима таймера 2 T2MOD

1 2 3 4 5 6 7 ... 20 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |