|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Классические однокристальные микроконтроллеры 1 2 3 4 5 6 ... 20 ных при обращении к внешней памяти. При обращении к внешней памяти в SFR РО автоматически заносятся единицы во все биты. Информация в SFR Р2 при этом остается неизменной. Отметим также, что для того, чтобы выводы порта РЗ выполняли альтернативные функции, необходимо в SFR РЗ также занести единицы во все биты. Выходы триггеров SFR портов Р1...РЗ выполнены на полевьпс транзисторах, имеющих внутреннюю нагрузку, в то время как вьпсоды триггеров SFR РО выполнены на транзисторах с открытым стоком. Каждая линия любого из портов может независимо использоваться как для ввода информации, так и для вывода (для линий портов РО и Р2 это справедливо тогда, когда они не используются для обращения к внешней памяти). Для использования любой линии портов Р1...РЗ в качестве входной необходимо в соответствующий разряд SFR занести 1. При этом выходной полевой транзистор отключается. Внутренний нагрузочный резистор как бы подтягивает потенциал вывода к напряжению питания, в то время как внешняя нагрузка может сделать его нулевым. Выводы порта РО имеют иную структуру. Нагрузочный полевой транзистор линии порта включен только тогда, когда порт выводит единицу при обращении к внешней памяти. В остальных случаях нагрузочный транзистор отключен. Таким образом, при работе в режиме обычного ввода/вывода информации (как, например, порт Р1) выводы порта РО представляют из себя транзисторы с открытым стоком. Запись единицы в соответствующий бит SFR отключает и второй транзистор. Это приводит к тому, что вывод оказывается под плавающим потенциалом. Это позволяет использовать линии порта РО как выводы с высокоимпедансным состоянием. Поскольку выводы Р1-РЗ имеют внутреннюю нагрузку, то при переводе их в режим ввода они являются источниками тока для выхода микросхемы или транзистора, нагруженного на этот вывод. Поэтому порты Р1-РЗ получили название квазидвунаправленные , в отличие от истинно двунаправленного порта РО, переводимого в режиме ввода информации в высокоимпедансное состояние. Каждый из выводов портов Р1-РЗ может быть нагружен начеты-ре ТТЛШ-входа (микросхемы серии К555). Они не требуют внешней нагрузки, но если в качестве выходов к этим выводам подключены ненагруженные выводы с открытым коллектором ими стоком, время установления сигнала может затянуться. Выводы порта РО при обращении к внешней памяти могут быть нагружены на восемь ТТЛШ-входов. При использовании в качестве обычного порта каждый из выводов должен быть подключен к шине питания через резистор номиналом 10...20 кОм. При использовании РО в качестве шины адреса/данных необходимость в этом отпадает. Во время выполнения команд, изменяющих SFR портов, новые значения защелкиваются в триггеры SFR в самом последнем цикле выполнения команды. Но на выводах микро-ЭВМ данные появляются только в начале выполнения следующей команды. Если это изменение представляет из себя перепад из О в 1 линий портов Р1-РЗ, то в начальный момент выполнения команды включается дополнительный нагрузочный транзистор в нагрузке транзистора выходного каскада порта. Дополнительная нагрузка в состоянии обеспечить ток переключения в 100 раз больший, чем номинальная, что резко повышает скорость переключения. В п-МОП версии обычная нагрузка обеспечивает ток через закороченный транзистор выходного буфера на уровне 0,25 мА. Дополнительная нагрузка обеспечивает ток при закороченном транзисторе до 30 мА. В к-МОП версии нагрузка выходного буфера состоит из трех полевых транзисторов. При установке на затворе транзистора единицы п-канальный полевой транзистор открывается, закрываясь при установке на затворе нуля, р-канальный полевой транзистор работает в противофазе с ним. При своем открывании п-канальный транзистор открывает через специальный инвертор дополнительный р-канальный транзистор. Отметим, что если на выводе микро-ЭВМ присутствовала 1, а внешняя нагрузка переключилась в ноль, то дополнительный нагрузочный транзистор может закрыться, и порт перейдет в высокоимпедансное состояние. Но при снятии причины, приведшей к этому переключению, основной р-канальный полевой транзистор, быстродействие которого велико и сопоставимо с быстродействием п-ка-нального, восстановит исходный потенциал. Обращение к портам ввода/вывода возможно с использованием команд, оперирующих с байтом, отдельным битом и произвольной комбинацией бит. При этом в тех случаях, когда порт является одновременно операндом и местом назначения результата, автоматически реализуется специальный режим чтение-модификация-запись . Этот режим обращения предполагает ввод сигналов не с внешних выводов порта, а из его регистра-защелки SFR, что позволяет исключить неправильное считывание ранее выведенной информации. Причиной, по которой оказалось необходимым осуществить команды типа чтение-модификация-запись , является необходимость исключить неправильное считывание уровня сигнала на выводе микро-ЭВМ. Предположим, например, что линия X порта Y соединяется с базой мощного транзистора, и выходной сигнал на ней предназначен для его управления. Когда в данный бит записана 1, то транзистор включается. Если для проверки состояния исполнительного ме- ханизма, управляемого мощным транзистором, прикладной программе требуется прочитать состояние выходного сигнала в том же бите порта, то считывание сигнала с внешнего вывода порта, а не из D-триггера SFR порта приведет к неправильному результату. Единичный сигнал на базе транзистора имеет относительно низкий уровень и будет интерпретирован CPU микро-ЭВМ как 0. Команды типа чтение-модификация-запись реализуют считывание из регистра SFR, а не с внешнего вывода порта, что обеспечивает получение правильного значения 1. Механизм чтение-модификация-запись реализован в командах ANL; ORL; XRL; JBC; CPL; INC; DEC; DJNZ; MOVPX.Y.C; CLR PX.Y; SETB PX. Y. В настоящем разделе мы только перечислили команды. Более подробно о них будет сказано позже. РАБОТА С ВНЕШНЕЙ ПАМЯТЬЮ Если используется 16-битовый адрес, старшие 8 бит выводятся через порт Р2, где они сохраняются в течение всего цикла обращения к внешней памяти. Отметим, что выходные буферы порта Р2 имеют внутреннюю нагрузку, несколько отличную от Р1 и РЗ, благодаря чему в SFR Р2 при выводе адресной информации вовсе не обязательно защелкивать все единицы. Добавим также, что при выводе адресной информации информация из SFR Р2, хоть и не присутствует на выводах микро-ЭВМ, но и не теряется, восстанавливаясь на выводах после окончания обращений к внешней памяти (если в процессе этих обращений SFR Р2 не был модифицирован). Если при обращении к внешней памяти данных используется 8-битный адрес, то на выводах порта остается та же информация, которая там была до начала обращения к внешней памяти. Это позволяет организовать постраничную адресацию внешней памяти данных. Во время обращения к внешней памяти CPU записывает OFFH в SFR РО, уничтожая, таким образом, хранимую там информацию. Следовательно, использовать для записи порт РО при работе с внешней памятью надо с известной долей осторожности. Обращение к внешней памяти программ возможно в двух случаях; сигнал ЕА активен, т. е. имеет нулевой уровень или программный счетчик PC содержит число больше OFFFH. Когда CPU работает с внешней памятью программ, все линии Р2 используются для вывода старшего байта адреса и не могут быть использованы для обычного ввода/вывода информации. При этом, как отмечалось выше, в SFR Р2 может быть занесена любая информация - адресная информация, выводимая через Р2, не зависит от состояния его SFR. УСТРОЙСТВО УПРАВЛЕНИЯ И СИНХРОНИЗАЦИИ К выводам XI и Х2 микро-ЭВМ подключается кварцевый резонатор. Об устройстве встроенного тактового генератора микро-ЭВМ будет рассказано ниже, при описании режимов энергопотребления. Пока отметим только то, что вырабатываемые им сигналы синхронизуют всю работу микро-ЭВМ. Устройство управления микро-ЭВМ формирует машинный цикл фиксированной длительности, равной 12 периодам резонатора или шести состояниям управляющего устройства (S1...S6). Каждое состояние содержит две фазы сигналов резонатора (Р1 и Р2). В фазе Р1,как правило, выполняется операция в АЛУ, а в фазе Р2 выполняется межрегистровая передача. Весь машинный цикл состоит из 12 фаз, начиная от S1P1 и кончая S6P2 (рис. 4). Этот рисунок иллюстрирует работу управляющего устройства при вьшолнении команд различной степени сложности - от однобайтовых, выполняющихся за один машинный цикл, до двухбайтовых, работающих с внешней памятью. Отметим, что заштрихованные сигналы являются внутренними, недоступными разработчику. Единственными внешними, наблюдаемыми сигналами являются сигналы кварцевого резонатора и сигналы ALE. Последние формируются дважды за один машинный цикл в фа- ® ® S1 Р1 Р2 1тени( КОПа !тени( КОПа 1тени( КОПа S2 Р1 Р2 S3 Р1 P2P1IP2P1 ющего КОПа (о -брас! шается) Чтеь ле байта ком; S6 Р2 КОПов (( КОПов (с S2 Р1Р2 S3 Р1 Р2 Чт( ние КОПа сл( дующей кaiaнды Чтение КОПа сл[ дующей кок^анды Чтени! i след ющих Чтение след ющих тбдас >1вается) тбдас )1вается) Обращение Нет ALE к внешней памяти данных S4 Р1 Р2 fir jIj S6 Р1Р2 S1 Р1Р2 Чте ние К( 1Па следук щей команды ЧтфиеКОПа следукЛцейк Рис. 4 3axSlP2-S2Pl и84Р2-55Р1.0ни используются процессором микро-ЭВМ для защелкивания младшего байта адреса при обращении к внешней памяти. Отметим только, что при обращении к внешней памяти данных сигнал ALE, вырабатываемый в фазе S1P2-S2P1 второго машинного цикла, отсутствует, т. к. в этот момент происходит передача дан- ных через линии порта РО, и защелкивание этой информации в регистре-защелке младшего байта адреса приведет к сбою системы. Количество машинных циклов и тактов, необходимое микро-ЭВМ для выполнения каждой команды, будет дано при описании системы команд. Сейчас отметим только, что микро-ЭВМ оперирует с 13 различными типами команд, имеющими длину от 1 до 3 байт и выполняющимися за 1...2 машинных цикла (за исключением двух однобайтовых команд умножения и деления, выполняющихся за 4 цикла). Таким образом, при работе на частоте 12 МГц подавляющее большинство команд выполняется микро-ЭВМ за 1...2 мкс, в связи с чем микро-ЭВМ рассматриваемого семейства превосходят по производительности системы на микропроцессоре 580ВМ80. На рис. 5-8 приведены временные диаграммы работы микро-ЭВМ с внешней памятью программ и данных и с портами ввода/вывода. При обращении к внешней памяти данных используются команды, выполняющиеся за два машинных цикла. В первом машинном цикле сигнал ALE возникает в момент S1P2 (на рис. 5, 6 не показаны) S4 S5 S6 Sr 1р1Р2Р11Р2Р1р2РГР2 S2 1IP2 rljlx jIj S4 !р1Р2 pol OUT (если нет обращния Данные действительны к внешней памяти)

S6 iP1P2 S2 Р1!Р2 S3 Р11Р2 S5 Р11Р2 ALE. pclout (если нет обращния к внешней памяти)

Рис. 6 81 82 s3 s4 I 85 p1p2p1p2 p1p2p1p2p1 ip2p1 P1P2 psbn. Данные действительны

pchout pch out pchout Рис. 7 Данные действительны: ДляР0,Р1,Р2,РЗ ДляР0,Р1,Р2,РЗ ДляR8T Для RST mov. port, 8RC ош data NEW DATA Сдвиг последовательного поста (оеж 01 Данные действигельны: порта 1реж.и) на входе RXD в буфере Рис. 8 И в момент S4P2 (первые из показанных на временных диаграммах рис. 5, 6). По спаду этих сигналов во внешний регистр-защелку должна быть занесена адресная информация, выводимая по линиям порта О (DPL OR RI OUT - вывод младшего байта из регистра DPTR, либо байта из регистра R0 или R1). При обращении к внешней памяти с использованием регистра DPTR на линиях порта 2 при этом появляется старший байт из регистра DPTR (DPH). Если происходит обращение к внешней памяти данных с использованием регистров R0 или R1, то на линиях порта появляется информация из его SFR (Р2 SFR OUT). В момент S1P1 второго машинного цикла активизируется сигнал RD или WR. При этом в режиме чтения линии порта переходят в высокоимпедансное состояние (FLOAT), и к моменту S3P1, когда микро-ЭВМ считывает данные, они должны быть установившимися (DATA SAMPLED). В режиме записи в течение всего времени действия сигнала WR на линиях портов сохраняется выво- 915995599�19 димая информация. В момент S1P1 второго машинного цикла как при чтении (рис. 5), так и при записи (рис. 6) сигнал ALE отсутствует, так как по линиям порта РО идет обмен данными между микро-ЭВМ и внешним ОЗУ, а не выводится адресная информация. При обраш,ении к внешней памяти программ (равно как и во всех остальных случаях, за исключением вышеупомянутых случаев обмена информацией с внешним ОЗУ) сигнал ALE формируется как в момент S1P2, так и в момент S4P2 без пропусков. Поскольку при об-раш;ении к внешней памяти программ всегда используется двухбайтовый счетчик команд PC, то его младший байт выводится по линиям порта РО (PCL OUT на рис. 7) и фиксируется во внешнем регистре-заш;елке по спаду ALE, а старший байт выводится по линиям порта Р2 (РСН OUT). Роль строб-сигнала чтения в этом случае играет сигнал PSEN. Временные диаграммы работы портов при вводе и выводе информации приведены на рис. 8. При вводе информации через порты РО-РЗ данные должны быть установившимися к моменту S5P1 и сохраняться неизменными до момента S5P2. При выводе информации из портов новые данные (NEW DATA) появляются на выводах микро-ЭВМ в момент SIP] цикла, следуюш;его за циклом, в котором осуществлялась команда вывода. Временные зависимости, относящиеся к последовательному порту (SERIAL PORT), будут описаны ниже. ТАЙМЕРЫ-СЧЕТЧИКИ Два программируемых 16-битных таймера-счетчика (Т /СО и Т /С1) могут быть использованы как в качестве таймеров, так в качестве счетчиков внешних событий. При работе в качестве таймера содержимое соответствующего Т /С инкрементируется в каждом машинном цик- ле, т. е. через каждые 12 периодов резонатора. При работе в качестве счетчика содержимое Т /С инкрементируется под воздействием перехода из 1 в О внешнего входного сигнала, подаваемого на соответствующий (ТО, Т1) вывод 8051. Опрос значения внешнего входного сигнала выполняется в момент времени S5P2 каждого машинного цикла. Содержимое счетчика будет увеличено на 1 в том случае, если в предыдущем цикле был считан входной сигнал высокого уровня (1), а в следующем - сигнал низкого уровня (0). Новое (инкремен-тированное) значение счетчика будет сформировано в момент S3P1 в цикле, следующем за тем, в котором был обнаружен переход сигнала из 1 в 0. Так как на распознавание перехода требуется два машинных цикла, то максимальная частота подсчета входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигна- лов ограштчений сверху нет. Для гарантированного прочтения входного считываемого сигнала он должен удерживать значение 1 как минимум в течение одного машинного цикла 8051. Для управления режимами работы Т 1С и для организации взаимодействия таймеров с системой прерыва1{ия используются два регистра специальных функций (Т MOD и Т CON), описание которых приводится в табл. 4 и 5 соответствен но. Как следует из описания управляющих бит ТМООдля обоих Т/С режимы работы О, I и 2 од1шако вы. Режимы 3 для Т /СО и Т /С1 различны. Рассмотрхтм кратко работу Т /С во всех четырех режимах. Таблица 4 Регистр режима работы таймер/счетчика TMOD

Примечание к таблице 4

Регистр управления/статуса таймера TCON

Режим 0. Перевод любого Т /С в режим О делает его похожим на таймер 8048 (8-битный счетчик), на вход которого подключен 5-битный предделитель частоты на 32. Работу Т /С в режиме О на примере Т /С1 иллюстрирует рис. 9, а. В этом режиме таймерный регистр имеет разрядность 13 бит. При переходе из состояния все единицы в состояние все нули устанавливается флаг прерывания от таймера TF1. Входной синхросигнал таймера 1 разрешен (поступает на вход Т /С1), когда управляющий бит TR1 установлен в 1 и либо управляющий бит GATE (блокировка) равен О, либо на внешний вывод запроса прерывания INT1 поступает уровень 1. Отметим попутно, что установка бита GATE в 1 позволяет использовать таймер для измерения длительности импульсного сигнала, подаваемого на вход запроса прерывания. Режим 1. Работа любого Т /С в режиме 1 такая же, как и в режиме О, за исключением того, что таймерный регистр имеет разрядность 16 бит. Режим 2. В режиме 2 работа организована таким образом, что переполнение (переход из состояния все единицы в состояние все  - TF1 Прерывание Вывод БИС БитСАТЕ liNTT Вывод БИС Вывод БИС БитСАТЕ БитСД INTr- Вывод БИС (Вбит) Управление Прерывание Перезагрузка (8 бит) Вывод БИС БитСД БитТВО rj БитСАТЕ Вывод БИС

TLO (8 бит) Прерывание Bm-TRl .

Прерывание Рис. 9 нули ) 8-битного счетчика TL1 приводит не только к установке флага TF1 (рис. 9, б), но и автоматически перезагружает в ТЫ содержимое старшего байта (ТН1) таймерного регистра, которое предварительно было задано программным путем. Перегрузка оставляет содержимое ТН1 неизменным. В режиме 2 Т /СО и Т /С1 также работают совершенно одинаково. Режим 3. В режиме 3 Т/СО и Т/С1 работают по-разному. Т/С1 сохраняет неизменным свое текущее содержимое. Иными словами, эффект такой же, как и при сбросе управляющего бита TR1 в нуль. Работу Т /СО в режиме 3 иллюстрирует рис. 9, в. В режиме 3 TLO и ТНО функционируют как два независимых^8-битных счетчика. Работу TLO определяют управляющие биты Т/СО (С/Т, GATE, TRO), входной сигнал INTO и флаг переполнения TFO. Работу ТНО, который может выполнять только функции таймера (подсчет машинных циклов микро-ЭВМ), определяет управляющий бит TR1. При этом ТНО использует флаг переполнения TF1. Режим 3 используется в тех случаях применения 8051, когда требуется наличие дополнительного 8-битного таймера или счетчика событий. Можно считать, что в этом режиме 8051 имеет в своем составе три таймера/счетчика. Если Т /СО используется в режиме 3, Т /С1 может быть выключен, переведен в режим 0,1 или 2 или может быть использован последовательным портом в качестве генератора частоты передачи. СИСТЕМА ПРЕРЫВАНИЙ Упрощенная схема прерываний 8051 показана на рис. 10. Вывод БИС БитТГО I V

I Бит ITO Детеетор спада Вывод БИС БитТР1 MUX Н - Jim-IT 1 Детектор спада 03 н овн 13Н 23 Н Рис. 10 Внешние прерывания INTO и INT1 могут быть вызваны либо уровнем, либо переходом сигнала из 1 в О на входах 8051, в зависимости от значений управляющих бит ITO и IT1 в регистре TCON. От внешних прерываний устанавливаются флаги IEO и IE1 в регистре TCON, которые инициируют вызов соответствующей программы обслуживания прерывания. Сброс этих флагов выполняется аппара-турно только в том случае, если прерывание было вызвано по переходу (срезу) сигнала. Если же прерывание вызвано уровнем входного сигнала, то сбросом флага IE должна управлять соответствующая подпрограмма обслуживания прерывания путем воздей ствия на источник прерывания с целью снятия им запроса. Флаги запросов прерывания от таймеров TFO и TF1 сбрасываются автоматически при передаче управления подпрограмме обслуживания. Флаги запросов прерывания RI и TI устанавливаются блоком управления приемопередатчика аппаратно, но сбрасываться должны программным путем. Прерывания могут быть вызваны или отменены программой, так как все перечисленные флаги программно-доступны и могут быть ус- тановлены/сброшены программой с тем же результатом, как если бы они были установлены/сброшены аппаратными средствами. В блоке регистров специальных функций есть два регистра, предназначенных для управления режимом прерываний и уровнями приоритета. Форматы этих регистров, имеющих символические имена IF и IP, описаны в табл. 6 и 7 соответственно. Возможность программной установки/сброса любого управляющего бита в этих двух регистрах делает систему прерываний 8051 исключительно гибкой. Таблица 6 Регистр масок прерывания (IE)

Таблица 7 Регистр приоритетов прерываний IP

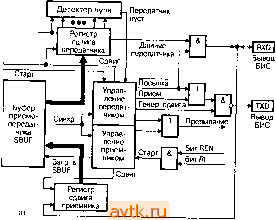

Флаги прерываний опрашиваются в момент S5P2 каждого машинного цикла. Ранжирование прерываний по уровню приоритета выполняется в течение следующего машинного цикла. Система прерываний сформирует аппаратный вызов (LCALL) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий : 1)в данный момент обслуживается запрос прерывания равного или высокого уровня приоритета; 2) текущий машинный цикл - не последний в цикле выполняемой команды; 3) выполняется команда RETI или любая команда, связанная с обращением к регистрам IE или IP. Отметим, что если флаг прерывания был установлен, но по одному из перечисленных выше условий не получил обслуживания и к моменту окончания блокировки уже был сброшен, то запрос прерывания теряется и нигде не запоминается. По аппаратно-сформированному коду LCALL система прерывания помещает в стек только содержимое счетчика команд (PC) и загружает в счетчик команд адрес вектора соответствующей подпрограммы обслуживания. По адресу вектора должна быть расположена команда безусловной передачи управления (JMP) к начальному адресу подпрограммы обслуживания прерывания. Подпрограмма обслуживания в случае необходимости должна начинаться командами записи в стек (PUSH) слова состояния программы (PSW), аккумулятора, расширителя, указателя данных и т. д. и должна заканчиваться командами восстановления из стека (POP). Подпрограммы обслуживания прерывания должны завершаться командой RETI, по которой в счетчик команд перезагружается из стека сохраненный адрес возврата в основную программу. Команда RET также возвращает управление прерванной основной программе, но при этом не снимает блокировку прерываний, что приводит к необходимости иметь программный механизм анализа окончания процедуры обслуживания данного прерывания. ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС Через универсальный асинхронный приемопередатчик осуществляется прием и передача информации, представленной последовательным кодом (младшими битами вперед), в полном дуплексном режиме обмена. В состав приемопередатчика, называемого часто последовательным портом, входят принимающий и передающий сдвигающие регистры, а также специальный буферный регистр (SBUF) приемопередатчика. Запись байта в буфер приводит к автоматичес- кой переписи байта в сдвигающий регистр передатчика и инициирует начало передачи байта. Наличие буферного регистра приемника позволяет совмещать операцию чтения ранее принятого байта с приемом очередного байта. Но если к моменту окончания приема байта предыдущий байт не был считан из SBUF, то он будет потерян. Последовательный порт 8051 может работать в четырех различных режимах. Режим 0. В этом режиме информация и передается, и принимается через внешний вывод входа приемника (RXD). Принимаются или передаются 8 бит данных. Через внешний вывод выхода передатчика (TXD) выдаются импульсы сдвига, которые сопровождают каждый бит. Частота передачи бита информации равна 1/12 частоты резонатора. Режим 1. В этом режиме передаются через TXD или принимаются из RXD 10 бит информации: старт-бит (0), 8 бит данных и стоп-бит (1). При приеме информации в бит RB8 регистра управления-статуса приемопередатчика SCON заносится стоп-бит. Скорость приема/передачи - величина переменная и задается таймером. Режим 2. В этом режиме через TXD передаются или из RXD принимаются И бит информации: старт-бит, 8 бит данных, программируемый девятый бит и стоп-бит. При передаче девятый бит данных может принимать значение О или 1, либо, например, для повышения достоверности передачи путем контроля по четности в него может быть помещено значение признака паритета из слова состояния программы (PSW.O). При приеме девятый бит данных помещается в бит RB8 SCON, а стоп-бит, в отличие от режима 1, теряется. Частота приема/передачи выбирается программой и может быть равна либо 1/32, либо 1/64 частоты резонатора в зависимости от управляющего бита SMOD. Режим 3. Режим 3 совпадает с режимом 2 во всех деталях, за исключением частоты приема/передачи, которая является величиной переменной и задается таймером. Во всех случаях передача инициализируется инструкцией, в которой данные перемещаются в SBUF. Прием инициализируется при обнаружении перепада из 1 в О на входе приемника. При этом в режиме О этот переход должен сопровождаться выполнением условий RI=0 и REN=1 (табл. 8), а для остальных режимов REN=1. Управление режимом работы приемопередатчика осуществляется через специальный регистр с символическим и.менем SCON. Этот регистр содержит не только управляющие биты, определяющие режим работы последовательного порта, но и девятый бит принимаемых или передаваемых данных (RB8 и ТВ8) и биты прерывания приемопередатчика (RI и TI). функциональное назначение бит регистра управления/статуса приемопередатчика приводится в табл. 8. Таблица 8 Регистр управления/статуса SCON

Примечание к таблице 8

Прикладная программа путем загрузки в старшие биты регистра SCON 2- битного кода определяет режим работы приемопередатчика. Во всех четырех режимах работы передача инициализируется любой командой, в которой буферный регистр SBUF указан как получатель байта. Как уже отмечалось, прием в рел<име О осуществляется при условии, что RI=0 и REN=1, в остальных режимах REN=1. В бите ТВ8 программно устанавливается значение девятого бита данных, который будет передан в режиме 2 или 3. В бите RB8 фикси- руется в режимах 2 и 3 девятый принимаемый бит данных. В режиме 1 в бит RB8 заносцтся стоп-бит. В режиме О бит RB8 не используется. Флаг прерывания передатчика TI устанавливается аппаратно в конце периода передачи стоп-бита во всех режимах. Соответствующая подпрограмма обслуживания прерывания должна сбрасывать бит TI. Флаг прерывания приемника RI устанавливается аппаратно в конце периода приема восьмого бита данных в режиме О и в середине периода приема стон-бита в режимах 1, 2 и 3. Подпрограмма обслуживания прерывания должна сбрасывать бит RI. Скорость приема/передачи, т. е. частота работы приемопередатчика в различных режимах, определяется различными способами. В режиме О частота передачи зависит только от резонансной частоты кварцевого резонатора i: f = fJU. За машинный цикл последовательный порт передает один бит информации. В режимах 1,2 и 3 скорость приема/передачи зависит от значения управляющего бита SMOD в регистре специальных функций PCON (табл. 9). Таблица 9 Регистр управления мощностью PCON

Примечание. При одновременной записи 1 в PD и IDL бит PD имеет преимущество. Сброс содержимого PCON выполняется путем загрузки в него кода ОХХХОООО В режиме 2 частота передачи определяется значением SMOD. При SMOD=0 частота передачи равна (1/64)£р^з, а при SM0D=1 равна (l/32)fp3, или в общем виде f=(2SMOD);(64xfpJ. В режимах 1 и 3 в формировании частоты передачи кроме управляющего бита SMOD принимает участие таймер 1. При этом частота передачи зависит от частоты переполнения f qvlti определяется следующим образом: f(2smod)x{fj, /32). Прерывание от таймера 1 в этом случае должно быть заблокировано. Сам же таймер может работать при этом как в режиме таймера, так и в режиме счетчика. Номер режима (О, 1, 2) роли не играет. Однако наиболее типичным является его использование в режиме таймера с автоперезагрузкой (старшая тетрада TMOD=0010B). При этом частота передачи определяется выражением: f (2 SMOD) X ( J / {32 X 12 X [256 ~ (ТН1)]}. В табл. 10 приводится описание способов настройки Т /С1 для получения типовых частот передачи данных через приемопфедатчик. Отметим, что скорость приема и передачи могут отличаться друг от друга. Таблица 10 Настройка таймера 1 для управления частотой работы приемопередатчика

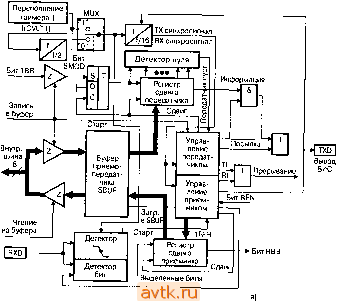

Предельно низких частот приемопередачи можно достичь при использовании таймера в режиме 1 (16-битовый таймер) и разрешении прерываний от таймера (старший полубайт TMOD = 0001В). Перезагрузка 16-битового таймера должна осуществляться программным путем. Перечислим особенности работы приемопередатчика в различных режимах. На рис. 11 показаны упрощенная структурная схема приемопередатчика и временная диаграмма его работы в режиме 0. Данные Запись в буфер

Внутр. гЪ шина I Чтение из буфера  S6I S5 S2S4S6I S2S4S6I S1S3S5 S1 S3S5 Передача S2S4S6 S2S4S6 S2S4S6 S2S4S6 S2S4S6I IS1S3S5 S1S3S5 S1S3S5 S1 S3S5 S1 S3S5 исьв SBUF S2S4S6 S2S4S6I IS1S3S5 S1S3S5 S2S4 S1 S3S5 -n-JLn JLJUULJlJUUnJL Запись в Посылка Сдвиг RXD. TXD. -Л-п П П П П П л. л IXIII3CKIXI21I>CIm3C2lI J?M~L rn J-bJ-n r-LJ--L r S3P1 Сброс RI П Прием Прием Сдвиг. RXD. TXD. -П-п-П-п п п п л. S5P21J LJ-l r U-L r-l J-L r Рис. 11 передаются и принимаются через вывод RXD. Через вывод TXD выдаются синхросигналы сдвига. Передаются/принимаются 8 бит, младшим битом вперед, частота обмена - фиксированная, равная 1/12 частоте резонатора. Передача начинается любой командой, по которой в SBUF поступает байт данных. В момент времени S6P2 устройство управления 8051 по сигналу Запись в буфер записывает байт в сдвигающий регистр передатчика, устанавливает триггер девятого бита и запускает блок управления передачей, который через один машинный цикл вырабатывает внутренний разрешающий сигнал Посылка . При этом в момент S6P2 каждого машинного цикла содержимое сдвигающего регистра сдвигается вправо (младшими битами вперед) и поступает на выход RXD. В освобождающиеся старшие биты сдвигающего регистра передатчика записываются нули. При получении от детектора нуля сигнала Передатчик пуст блок управления передатчиком снимает сигнал Посылка и устанавливает флаг TI (момент S1P1 десятого машинного цикла после поступления сигнала Запись в буфер ). Прием начинается при условии REN=1 и R1=0. В момент S6P2 следующего машинного цикла блок управления приемником формирует разрешающий сигнал Прием , по которому на выход TXD передаются синхросигналы сдвига и в сдвигающем регистре приемника начинают формироваться значения бит данных, которые счи-тываются с входа RXD в моменты S5P2 каждого машинного цикла. В момент S1P1 десятого машинного цикла после сигнала Запись в SCON блок управления приемником переписывает содержимое сдвигающего регистра в буфер, снимает разрешающий сигнал Прием и устанавливает флаг RI. На рис. 12 показаны структурная схема и временные диаграммы работы приемопередатчика при приеме и передаче данных в режиме 1. Через выход TXD приемопередатчик передает, а со входа RXD принимает 10 бит: старт-бит (0), 8 бит данных и стоп-бит (1). При приеме стоп-бит поступает в бит RB8 регистра SCON. Передача инициируется любой командой, в которой получателем байта является регистр SBUF. Генерируемый при этом управляющий сигнал Запись в буфер загружает 1 в девятый бит сдвигающего регистра передатчика, запускает блок управления передачей и в момент времени S1P1 формирует разрешающий сигнал Посылка . По этому сигналу на вывод TXD сначала поступает старт-бит, а затем (по внутреннему разрешающему сигналу Данные ) биты данных. Каждый период передачи бита равен 16 тактам внутреннего счетчика-делителя на 16. Прием начинается при обнаружении перехода сигнала на входе RXD из состояния 1 в состояние 0. Для этого под управлением внутреннего счетчика вход RXD опрашивается 16 раз за период представления бита. Как только переход из 1 в О на входе RXD обнаружен, в сдвигающий регистр приемника загружается код 1FFH, внутренний счетчик по модулю 16 немедленно сбрасывается и перезапускается для выравнивания его переходов с границами периодов представления принимаемых бит. Таким образом, каждый период представле- Переброс  Вывод БИС Опрос входного сигнала ТК синхро- П сигнал - *-Запись в Г SBUF- Л-fI Jl JL Передача п л л п п Посылка Данные Сдвиг TXD- 151Р1 л п п Jl-fl-JL Старт-бит Стоп-бит RX синхросигнал - RXD- Опрос входного ситала Пересброс JLLfL Прием Л п -П-л п я л JILJIUIIIILJIIILJIIIUI Л-Jl fL Л Л n JL n Г Рис. 12 ния бита делится на 16 периодов внутреннего счетчика. В состояниях 7,8 и 9 счетчика в каждом периоде представления бита производится опрос сигнала на входе RXD; Считанное значение принимаемого бита - это то, которое было получено по меньшей мере дважды из трех замеров (мажоритарное голосование по принципу два из трех ). 1 2 3 4 5 6 ... 20 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |