|

|

|

Разделы

Публикации

Популярные

Новые

|

Главная » Классические однокристальные микроконтроллеры 1 2 3 4 5 ... 20 Усложним задачу. Пусть теперь нам нужно вычесть из числа 3 число 8 (т. е. в отличие от предыдущего случая результат вычитания должен оказаться отрицательным). Давайте опять заменим вычитание сложением - сложим десятичные числа +3 и -8. Согласно все той же табл. 10, -t-3 должно быть представлено в виде 0000 0011, а -8 в виде 1111 1000. Эти представления сложим, как обычные двоичные числа, что даст 1111 1011 = -5,о: 1-е число 2-е число (4-3) 0000 0011 + -t- (-8) nil 1000 (-5) 1111 1011. Как видим, и в этом случае сложение представленных с использованием дополнительного кода двух знаковых чисел, одно из которых положительно, а другое отрицательно, по-прежнему дало правильный результат. С учетом предыдущего, можно сказать, что если складывать представленные в дополнительном коде два знаковых числа, из которых хотя бы одно положительно, то независимо от знака полученной суммы результат сложения окажется правильным. И в заключение сложим два отрицательных десятичных числа: -2 и-5. Согласно табл. 10, -2 = 1111 1110 и-5 = 1111 1011. Два числа 1111 1110 и 1111 1011 складываются, как обычные двоичные числа, что дает 1 1111 1001 : 1-е число 2-е число (-2) + (-5) 1111 1110 + 11111011 (-7) 111111001 (пренебречь переполнением). Старший бит результата по-прежнему является переполнением 8-разрядного регистра, и им пренебрегаем. Таким образом, суммой двух чисел ПИПЮиИИЮИв дополнительном коде будет равна ИИ 1001. Согласно табл. 10, сумма ИИ 1001 - это ни что иное как-7,q. Таким образом, во всех рассмотренных случаях сложение представленных с использованием дополнительного кода двух знаковых чисел, независимо от того, положительные они или отрицательные, дает правильный результат, если сумма также рассматривается как число со знаком. А поскольку вычитание - это фактически сложе- ние двух чисел, одно из которых (вычитаемое) отрицательно, то оказывается, что микроконтроллер вообще может обойтись без команд вычитания - их с успехом заменяют команды сложения знаковых чисел, представленных в дополнительном коде. Еще несколько примеров для закрепления сказанного. Вычтем десятичное число +5 из десятичного числа +8. Уменьшаемое (+8) в дополнительном коде равно 0000 1000. Поскольку мы собираемся заменить вычитание сложением знаковых чисел в дополнительном коде, вместо вычитаемого (+5) мы должны взять равное ему по модулю отрицательное число (-5). В дополнительном коде оно равно 1111 1011 (инвертируем 0000 0101 и добавляем к полученному 1). Затем первое число 0000 1000 складывается со вторым 1111 1011 как с обычным числом, что дает 1 0000 0011: 1-е число 2-е число (+8) 0000 1000 Дополнительный код + (+5) 1111 1011 -= 0000 0101 > . (+3) 1 0000 0101 (пренебречь переполнением). Таким образом, чтобы заменить вычитание сложением, мы должны заменить вычитаемое на равное ему по модулю число с противоположным знаком, сложить с уменьшаемым и отбросить переполнение, если оно возникнет. Преобразование вычитаемого в равное ему по модулю число с противоположным знаком осуществляется путем его инвертирования (замены входящих в его двоичное представление единичных бит на нулевые и наоборот) с последующим прибавлением к полученному в результате инвертирования числу единицы. Вычтем десятичное число +6 из десятичного числа +2: 1-е число 2-е число (+2) 0000 0010 Дополнительный код + (+6) 1111 1010 -= 0000 0110 . (-4) 11111100 в соответствии с табл. 10, первое число +2 = 0000 0010, второе число +6 - 0000 ОНО, его дополнительный код (инверсия и добавление 1)- 1111 1010. Оба эти кода сложены затем, как обычные двоичные числа, что дает 11111100, а согласно табл. 10 И11 1100 = -4 Упражнения 38. Сложить следующие десятичные числа со знаком, используя метод дополнительного кода: а) (+7) б) (+31) + + (+1) (4-26). 39. Сложить следующие десятичные числа со зйаком, используя метод дополнительного кода: а) (+8) б) [+89) + + (-5) (-46). 40. Сложить следующие десятичные числа со знаком, используя метод дополнительного кода: а) (-П) б) (+20) + + (-6) (-60). 41. Сложить следующие десятичные числа со знаком, используя метод дополнительного кода: а) (-3) б) (-13) + + (-4) (-41). 42. Вычесть следующие десятичные числа со знаком, используя метод дополнительного кода: а) (-t-7) б) (-И13) (+2) (+50). 43. Вычесть следующие десятичные числа со знаком, используя метод дополнительного кода: а) (+3) б) (+12) (+8) (+63). Решения 38. Следовать процедуре, приведенной вразделе 7: а) (+7) 0000 0111 6) (+31) 0001 1111 + + + + (+1) 0000 0001 (+26) 0001 1010 (+8) 0000 1000 (доп. код); (+57) ООП 1001 (доп. код). 39. Следовать процедуре, приведенной вразделе 7: а) (+8) 00001000 6) (+89) 0101 1001 + + + + (-5) 1111 101 (-46) 1101 0010 (+3) 1 000 0011 (доп. код); (+43) 1 00101011 (доп. код). Пренебречь переполнением. Пренебречь переполнением. 40. Следовать процедуре, приведенной в разделе 7: а) (+1) 0000 0001 б) (+20)0001 1100 + + + + (-6) 1111 1010 (-60) 1100 0100 (-5) 11111011 (доп. код); (-40) 1101 1000 (доп. код). 41. Следовать процедуре, приведенной вразделе 7: а) (-3) 1111 1101 б) (-13) 1111 ООП + + + + (-4) 11111100 (-41) 11010111 (-7) 1 1111 1001 (доп. код); (-54) 1 11001010 (доп. код). Пренебречь переполнением. Пренебречь переполнением. 42. Следовать процедуре, приведенной вразделе 7: а) (+7) 0000 0111 (+2) дополнительный 1111 1110 (+5) = 0000 0010 код и сложить 1 0000 0101 (доп. код). Пренебречь переполнением. б) (+113) (+50) дополнительный 0111 0001 11001110 (+5) = 0011 0010 код и сложить 1 ООП 1110 (доп. код). Пренебречь переполнением. 43. Следовать процедуре, приведенной в разделе 7: а) (+3) (+8) (-5) б) (+12) (+63) (-51) = 00001000 дополнительный код и сложить = 0011 1111 дополнительный код и сложить 0000 0011 + 1111 1000 1111 1011 (доп. код). 00001100 + 1100 0001 11001101 (доп. код). 8. ГРУППИРОВКИ БИТ Одна О'щельная двоичная цифра называется битом, сгруппированных 4 бит составляют тетраду, 8 бит - байт. Входящий в состав микроконтроллера аккумулятор является очень важной частью всего МК. Обычно МК содержит 8-разрядный аккумулятор. Длина слова МК составляет тогда 8 бит, т. е. 1 байт составляет слово. Микроконтроллер имеет длину слова в 4,8,16 и даже 32 бит. Таким образом, 16-разрядный МК имеет длину слова 2 байта или 16 бит. Слово - это одна группа обрабатываемых бит, единое выражение или одна команда микропроцессора. Восьмиразрядный микроконтроллер переносит и помещает все данные группами из 8 бит, которые передаются восемью параллельными проводниками, составляющими ширину данных. На рис. 9, а приведено состояние, которое могла бы иметь память 8-разрядного микропроцессора, такого, как Intel 8080/8085 (КР580ВМ80). Заметим, что каждая адресуемая позиция (названная содержимым) составляет группу из 8 бит информации. Каждый байт называется запоминаемым словом, поскольку данный микропроцессор является 8-разрядным устройством. Каждое запоминаемое слово имеет особое значение, когда оно извлечено и декодировано микропроцессором. Содержимое памяти на рис. 9, а Адресная шина и линия управления Вход Порт) -<-/в-разрядный микропроцессор *-

Шина данных Выход Порт 10

Интерпретация микропроцессором слов памяти Код команды Ввести данные Двоичный адрес порта 1 . Код команды Разместить данные Двоичный адрес памяти Код команды Вывести данные Адрес порта 10 Код ASCII буквы А б) Рис. 9. Представление памяти микро-ЭВМ: а - типичное содержание; б - интерпретация содержимого МП может иметь один из следующих смыслов: 1) двоичное число; 2) двоичное число со знаком; 3) двоично-десятичное число; 4) буква алфавита; 5) команда; 6) адрес памяти; 7) адрес порта ввода или вывода. Рассмотрим верхнюю ячейку памяти на рис. 9, а, т. е. ячейку ОНО OlOOj. Ее содержимым является 1101 1011. Это двоичное слово могло бы быть интерпретировано как 1) двоичноечисло 1101 1011 = 219,; 2) двоичное число со знаком 1101 1011= -37, (здесь подразумевается дополнительный код); 3) двоично-десятичное число - это невозможно, так как ни 1101, ни 1011 не представляет двоично-десятичный код; 4) буква алфавита - это не соответствует ни одной букве кода ASCII (ASCII - широко распространенны буквенно-цифровой код, см. раздел 9.9); 5) командой; 1101 1011 - команда INPUT ( Ввести для хорошо известного процессора Intel 8080/8085 (КР580ВМ80); 6) адрес ячейки памяти 1101 10112 = DB,g =219,о; 7) адрес порта ввода или вывода 1101 10112 = 219,q . Если оператор МП Intel 8085 включит счетчик команд с адреса 100,0 (ОНО ОЮОД МП извлечет, затем декодирует слово в памяти 1101 1011 как команду Ввести (INPUT) данные. Затем он обратится к следующему адресу 101,0 (ОНО OlOlj), где расположен адрес порта, откуда нужно взять вводимые данные. В итоге, программа выполняет следующие команды: 1) Ввести (INPUT) данные, приходящие из порта 1; 2) Поместить (STORE) эти данные в ячейку памяти 200; 3) Вывести (OUTPUT) эти данные в порт 10. Способ, по которому МП интерпретирует содержимое ячеек памяти, детализирован на рис. 9, б. Команды программы помещены в шесть верхних ячеек (100-105). Нижняя ячейка памяти (200,о) является местом размещения данных. В этом случае код ASCII для буквы А помещен в эту ячейку памяти. В итоге важно отметить, что биты сгруппированы в слова внутри микропроцессора. Эти слова памяти программы интерпретируются микропроцессором одно за другим последовательно. Программисту очень важно знать, как микропроцессор располагает и интерпретирует данные. У каждого МП система команд уникальна, но у всех микропроцессоров доступ к ячейкам памяти осуществляется одинаково. Упражнения 44. Группа из 4 бит составляет тетраду, а группа из 8 бит - . 45. Длина является важной особенностью МП. Она соответствует числу передаваемых, обрабатываемых бит одной сущности. 46. Обратиться к рис. 9, а. Байт данных, помещенный в какую-либо ячейку памяти, называется словом . 47. Дать список семи возможных толкований 8-разрядного слова в памяти. 48. Как на рис. 9, б МП интерпретирует слово 0000 0001 по адресу 101,g? 49. Как на рис. 9, бМП. интерпретирует слово ООН 0111 по адресу 102,q? Решения 44. Байт. В некоторых случаях эта группаможет составлять такжеслово. 45. Слова. 46. Данных. 47. Двоичное число, двоичное число со знаком (записанное в дополнительном коде), двоично-десятичное число, буква алфавита, команда, адрес памяти, адрес порта в^ода/вывода. 48. Он извлекает запомненное слово, ожидая, что оно ему укажет, из какого порта он должен взять данные. Это слово укажет ему,что речь идет о порте 1. 49. Он извлекает слово ООП 0П1, ожидая новой команды. Это слово декодируется микропроцессором как команда Передать (MOVE) данные из аккумулятора в ячейку памяти, адрес которой приводится в следующей ячейке памяти. 9. БУКВЕННО-ЦИФРОВОЙ КОД Когда микроконтроллер взаимодействует с телетайпом или видеотерминалом, необходимо прибегать к коду, который одновременно включает в себя числовые и алфавитные знаки. Такие коды называются буквенно-цифровыми. Наиболее распространен буквенно-цифровой код ASCII (произносится АСКИ два) - стандартный американский код обмена информации. В табл. 11 приведена выдержка 7-разрядного кода ASCII. В этот список входят 7-разрядные коды цифр, прописных букв и знаков пунктуации. Полный код ASCII включает кодирование строчных букв и признаков команд. Таблица 11 Выдержка из алфавитно-цифрового кода ASCII

Упражнения 50. Двоичный код, используемый обычно для кодирования цифр и букв, называется кодом. 51. Нуль в коде ASCII представляется как 0110000,9 - как. х„ л-- 52. Если маскировать три старших разряда цифр от О до 9 в коде ASCII, что оставит маска в итоге? Решения 50. Буквенно-цифровым. 51. См. табл. 11:0111001. 52. Останется четыре немаскированнык бита, составляющих двоичный или двоично-десятичный эквивалент каждого числа (см. табл. 11). Дополнительные упражнения 53. Дать на память десятичные эквиваленты каждого из следуюидих двоичных чисел: а) 0000; б) 0010;в)0011;г) 0111;д) 1001;е) 1100. 54. 0110 lOOlj = . 55.60,0 =-. 56. Двоичное число 1001 1100 представляет собой число 9С в записи. 57.8 =-. 58.0101 11112 = - 59.AE,g =- 60. 1011 11002 = . 61.30,6 =- 62.90,0 =- 63.71308 = 64. 1001 0111 00102 = . 65. 578 =- 66.63,0 =- 67.92,0 = . 68. 1000 0110 ДЦК = . 69. Выполнить сложение следуюш;их двоичных чисел: а) 1100 ООП + ООН 1100; 6) ОНО 1110 + ООП 1101. 70. 1101 10002-0011 00112 = . 71. 10012*11012 = . - *-*2----/-- 72. Когда числа со знаком помеш;аются в регистр микропроцессора, 1 в старшем бите означает, что число (положительное, отрицательное). 73. Запись в дополнительном коде 1111 1110 представляет собой (отрицательное, положительное) число. 74. Записать следуюш;ие Десятичные числа со знаком в дополнительном коде: а)+12; 6)-12. 75. Записать следуюидие числа (в дополнительном коде) десятичными числами со знаком; а) 0111 0100; 6) 1101 1101. 76. Сложить следуюидие десятичные числа со знаком, используя метод дополнительного кода: а) (+13) б) (+17) в) (-6) + + + (+8) (-8) (-14). 77. Вычесть следуюш;ие десятичные числа со знаком, используя метод дополнительного кода: а) (-( 13) б) (-( 19) (+5) (+29). 78. Байт - это группа из. 79. Тетрада состоит из. бит. 80. Наиболее широко распространена длина слова микропроцессора . (8,32) бит. 81. См. рис. 9, а. На этом рисунке приведена функциональная схема (микропроцессора, микроконтроллера). 82. См. рис. 9, б. Как интерпретирует микропроцессор слово 1101 ООП по адресу 104,о? 83. Сокраидение ASCII читается по русски . 84. Для вывода на видеотерминал используется специальный код Решения 53. а) 0; 6) 2; в) 3; г) 7; д) 9; е) 12. 54. 105,д. 55. 1111002. 56. Шестнадцатеричной. 57. 10001101,. 58. 5F . 59. 10101110. 60 ВС 61.60, 62. 5А 63. 111001 OIIOOO2. 64. 4562. 65. 47, 66 77f.. 67.1001 ООЮддк. 68. 861д. 69. a) 1111 11112,6)10101011,. 70. 1010 0101,. 71. 1110101,. 72. Отрицательное. 73. Положительное. 74. а) 00001100; б) 1111 0100. 75. а)+116, 6)-35 , 76. а) 0001 0101 (доп. код); 6)11110110 (доп. код ); в) 11101100 (доп. код). 77. а) 00001000 (доп. код); б) 1111 ОНО (доп. код). 78. 8. 79. 4. 80 8. 81. Микроконтроллера. 82. Он извлекает из памяти слово 1101 ООП, полагая, что это новая команда. Слово 1101 ООП декодируется микропроцессором как команда ВЫВЕСТИ данные, содержаш,иеся в аккумуляторе, в порт, адрес которого будет находиться в следующей ячейке памяти. 83.Американский стандартный код обмена информацией АСКИ два. 84. ASCII или буквенно-цифровой. Приложение 2 КЛАССИЧЕСКИЕ МИКРОКОНТРОЛЛЕРЫ (ОДНОКРИСТАЛЬНЫЕ МИКРО-ЭВМ) СЕМЕЙСТВ MCS-51 И MCS-52 Первые микро-ЭВМ (серии 8048), едва появившись на западном рынке, сразу же завоевали симпатии разработчиков и потребителей. На них выполнялись десятки устройств - от счетчиков в такси до устройств управления технологическими процессами. Фирма IBM, разрабатывая свой знаменитый IBM-PC, встроила такую однокристальную микро-ЭВМ в клавиатуру, освободив, таким образом, центральный процессор от выполнения функций, связанных с ее обслуживанием. Вследствие этого в 80-х годах 20 столетия микро-ЭВМ этой серии стали наиболее массовыми из всех 8-разрядных микропроцессоров - за эти годы IBM-совместимых компьютеров было выпущено около 50 млн. штук, и выпуск их с каждым годом продолжал расти. Однако практически сразу были отмечены недостатки этих микро-ЭВМ. Разработчики постоянно ощущали нехватку объема ПЗУ, как встроенного, так и внешнего. Мал был объем ОЗУ: из 64 байт у 8748 почти половину занимали системные ресурсы - регистры и стек. Глубина стека была явно недостаточной для многих задач, равно как и разрядность встроенного таймера-счетчика. Не хватало портов ввода/вывода, отсутствовали простые аппаратные средства обмена информацией между микро-ЭВМ и другими ЭВМ. Ощущалась нехватка многих команд, в первую очередь вычитания. Словом, всего было мало, как с точки зрения аппаратных средств, так и с точки зрения программных. Перед разработчиками фирмы Intel стояла нелегкая задача - существенно доработать микро-ЭВМ, не выходя за пределу 256 команд и не увеличивая числа выводов ее корпуса. И они прекрасно справились с ней. Их новое детище - 8051 - на порядок превосхо- дил 8048 по производительности. Он имел вдвое большее ОЗУ, вдвое большее количество регистров общего назначения, четыре порта ввода/вывода, два таймера-счетчика и две линии прерываний. Имелись аппаратные средства для последовательного обмена информацией, был значительно увеличен объем ПЗУ, в том числе и внутреннего (для тех моделей семейства, которые его имели). В модели с УФ-ПЗУ 8751 появилось новшество -- бит защиты информации. Установка этого бита приводила к тому, что считать информацию из ПЗУ микро-ЭВМ становилось невозможным - свойство отнюдь не лишнее в условиях конкурентной борьбы. С появлением этих микро-ЭВМ семейство 8048 как бы отошло на второй план. Несмотря на продолжавшийся их выпуск и широкое использование в ранее разработанной аппаратуре, они почти сразу перестали служить основой для новых разработок (по крайней мере в тех странах, где микро-ЭВМ семейства 8051 были доступны разработчикам и производителям). Этому способствовало и то, что цены на микро-ЭВМ обоих семейств мало отличались друг от друга. Уже в 90-х микро-ЭВМ семейства 8051 стали доступными и отечественным пользователям. Поэтому приводимая ниже информация посвящена микропроцессорам этого семейства, а также последовавшего за ним семейства 8052. Однокристальные микро-ЭВМ семейства 8051 ВВЕДЕНИЕ В заголовке настоящего раздела автор не случайно упомянул семейство 8051. Дело в том, что отечественная промышленность так и не смогла по-настоящему освоить выпуск микро-ЭВМ этого семейства. Автору доводилось держать в руках микросхемы КМ1816ВЕ51, не имеющие УФ-ПЗУ. По-видимому, эти микросхемы можно рассматривать как аналоги микро-ЭВМ 8051 с ПЗУ, программируемым на заводе-изготовителе. При работе с ними необходимо использовать внешнее ПЗУ. Аналогичным образом используется микросхема ВЕ31. Обе эти микросхемы есть как в серии 1816, так и в серии 1830. Микро-ЭВМ серии 1816 выполнены по пМОП технологии, 1830 - по к-МОП. УФ-ПЗУ снабжена микросхема 1816ВЕ751 - аналог 8751. Однако ни автору настоящей статьи, ни его знакомым не доводилось видеть эту микросхему живьем . Думается, что и для радиолюбителей она вряд ли окажется доступной - сейчас легче приобрести 8751 или 87С51 (последняя является К-МОП модификацией 8751). Поэтому дальше о рассматриваемых микро-ЭВМ мы будем говорить, что они относятся к семейству 8051, указывая на различия между членами семейства в т^х случаях, когда это будет необходимо. К сожалению, в распоряжении автора статьи не было детального описания на отечественные микро-ЭВМ, подобного тому, которое выпускается фирмой Intel. Поэтому основным документом, который использовался автором при подготовке материалов, был Intel Databook, и все, что сказано про микро-ЭВМ рассматриваемого семейства, безусловно справедливо для микро-ЭВМ этого семейства зарубежного производства. Что касается отечественных микро-ЭВМ, то автор не рискует категорически утверждать, что все, о чем говорится в настоящем приложении, распространяется и на них. Но скорее всего это именно так. Во всяком случае, на момент подготовки статьи у автора не было данных о расхождении отечественных и зарубежных версий микро-ЭВМ. Все микро-ЭВМ семейства 8051 имеют следующие аппаратные особенности: наличие 128 байт внутреннего ОЗУ; наличие 4-х двунаправленных побитно настраиваемых 8-разрядных портов ввода/вывода; наличие двух 16-разрядных таймеров-счетчиков; встроенный тактовый генератор; адресация 64К памяти программ и 64К памяти данных; две линии запросов на прерывание от внешних устройств; интерфейс для последовательного обмена информацией с другими микро-ЭВМ или персональными компьютерами; микро-ЭВМ 8751 снабжена УФ-ПЗУ объемом 4К. Функциональная схема микро-ЭВМ семейства 8051 приведена на рис. I, назначение их выводов - на рис. 2. Кратко поясним приведенные на последнем обозначения: Vss - потенциал земли; Усе - основное напряжение +5 В; XI, Х2 - входы для подключения кварцевого резонатора; RST - вход общего сброса микро-ЭВМ; PSEN - разрешение внешней памяти программ; выдается только при обращении к внешнему ПЗУ; ALE - строб адреса внешней памяти; ЕА - отключение внутренней программной памяти; уровень О на этом входе заставляет микро-ЭВМ выполнять программу только внешнего ПЗУ, игнорируя внутреннее (если последнее имеется); Р1 - 8-битный квазидвунаправленный порт ввода/вывода; каждый разряд порта может быть запрограммирован как на ввод, так и на вывод, независимо от состояния других разрядов; Доп - ОЗУ 8052 т ОЗУ ПортРО ПортР2 Порт РО per. SFR т ПортР2 ПЗУ 4 per. SFR АЛУ PSEN , ALE, RST. Цепи управления и сброса

Рис. 1 т PCON SCON тно SBUF TMOD ПортР! per. SFR TOON DPTR Порт P3 per. SFR Порт P3 P1.0 - P1.1 PI.2 -P1.3-P1.4 P1.5-P1.6-P1.7 RST-(RXD) P3.0 (TXD) P3.1 - (INTO) P3.2 -(ШТТ) P3.3 (TO) P3.4 (T1)P3.5- (WR) P3.6 - -(RD) P3.7 <-X20-X1 o- -OUcc PO.O (ADO) P0.1 (ADl) P0.2(AD2) -f P0.3 (AD3) P0.4 (AD4) -* P0.5 (ADS) P0.6(AD6) P0.7 (AD7) -♦ALE -♦PSEN - P2.7 (A15) P2.6(A14) -♦ P2.5(A13) P2.4(A12) -> P2.3(A11) -♦ P2.2(A10) P2.1 (A9) -♦ P2.0(A8) P2 - 8-битный квазидвунаправленный порт, аналогичный PI; кроме того, выводы порта используются для выдачи адресной информации при обращении к внешней памяти программ или данных (если используется 16-битовая адресация последней). Выводы порта используются при программировании 8751 для ввода в микро-ЭВМ старших разрядов адреса; РЗ - 8-битный квазидвунаправленный порт, аналогичный Р1; кроме того, выводы порта могут выполнять ряд альтернативных функций, которые описаны ниже. РО - 8-битный двунаправленный порт ввода/вывода информации; при работе с внешними ОЗУ и ПЗУ по линиям порта в режиме временного мультиплексирования выдается адрес внешней памяти, после чего осуществляется передача или прием данных. ОРГАНИЗАЦИЯ ОЗУ, ПЗУ, РЕГИСТРОВ МИКРО-ЭВМ Рассмотрим более подробно внутреннее устройство микро-ЭВМ (рис. 1). Память программ и данных, также как и у микро-ЭВМ семейства 8048, являются самостоятельными и независимыми друг от друга устройствами, адресуемыми различными командами и управляющими сигналами. Объем памяти программ, расположенной на кристалле микро-ЭВМ 8051 и 8751, равен 4 кбайтам. При обращении к внешней памяти программ все микро-ЭВМ семейства 8051 всегда используют 16-разрядный адрес, что обеспечивает им доступ к 64К ПЗУ. Микро-ЭВМ обращается к программной памяти при чтении кода операции и операндов (используя счетчик команд PC), а также при выполнении команд переноса байта из памяти программ в аккумулятор. При выполнении команд переноса данных адресация ячейки памяти программ, из которой будут прочитаны данные, может осуществляться как с использованием счетчика PC, так и с использованием специального двухбайтового регистра-указателя данных DPTR. Память данных, расположенная на кристалле, имеет объем 128 байт. Первые 32 байта организованы в четыре банка регистров общего назначения, обозначаемых соответственно банк 0...3. Каждый банк состоит из 8 регистров R0...R7. В любой момент времени программе доступен только один банк регистров, номер которого содержится в 3-м и 4-м битах слова состояния программы PSW (см. ниже). Оставшееся адресное пространство может конфигурироваться разработчиком по своему усмотрению - в нем располагаются стек, системные и пользовательские области данных. Обращение к ячейкам памяти данных возможно двумя способами. Первый способ - прямая адресация ячейки памяти. В этом случае адрес ячейки является операндом соответствующей команды. Второй способ - косвенная адресация при помощи регистров R0 или R1. Перед выполнением соответствующей команды в один из этих регистров должен быть занесен адрес ячейки, к которой необходимо обратиться. К адресному пространству памяти данных примыкает адресное пространство регистров специальных функций SFR (табл. 1). Адреса, по которым расположены эти регистры, приведены ниже. Отметим, что регистры занимают только часть 128-байтового адресного пространства. Те ячейки памяти с адресами 80H...0FFH, которые не заняты регистрами, физически отсутствуют на кристаллах микро-ЭВМ семейства 8051, и при обращении к ним можно прочитать лишь код команды возврата. Таблица 1 Блок регистров специальных функций

Примечание. Регистры, имена которых отмечены знаком (*), допускают адресацию своих отдельных бит при выполнении команд из группы команд операций с битами. При обращении к внешней памяти данных микро-ЭВМ становятся доступными 64К ОЗУ. Адресация упомянутых ячеек внешнего ОЗУ осуществляется методом косвенной адресации при помощи регистров R0 и R1 или при помощи вышеупомянутого двухбайтового регистра DPTR. Аккумулятор является источником операнда и местом фиксации результата при выполнении ряда операций. Только с использованием аккумулятора могут быть выполнены операции сдвига, проверки на нуль и ряда других. Однако в отличие от большинства микропроцессоров, система команд 8051 содержит большое количество команд пересылок, логических операций и переходов, не использующих аккумулятор. В этом отношении упомянутая система команд гораздо гибче, чем система команд микропроцессора 580ВМ80. При выполнении ряда команд в арифметическо-логическом устройстве (АЛУ) формируются признаки операций - флаги, которые фиксируются в регистре PSW. Перечень флагов, их символические имена и условия их формирования приведены в табл. 2. Таблица 2 Формат слова состояния программы PSW

Регистр-указатель стека SP в микро-ЭВМ рассматриваемого семейства - 8-битный. Он может адресовать любую область внутренней памяти данных. В отличие от микропроцессора 580ВМ80, у семейства 8051 стек растет вверх , т. е. перед выполнением команды PUSH или CALL содержимое SP инкрементируется, после чего производится запись информации в стек. Соответственно при извлечении информации из стека регистр SP декрементируется после извлечения информации. в процессе инициализации микро-ЭВМ после сигнала сброса или при включении питающего напряжения в SP заносится код 07Н. Это означает, что первый элемент данных будет располагаться в ячейке памяти с адресом 08Н. Регистр-указатель данных DPTR чаще всего используется для фиксации 16-битного адреса в операциях обращения к внешней памяти программ и данных. С точки зрения программиста он может выступать как в виде одного 16-битного регистра, так и в виде двух независимых регистров DPL и DPH. Две регистровые пары с именами ТНО, TL0 и ТН1, TL1 представляют из себя регистры, обеспечивающие независимое функционирование двух программно-управляемых 16-битных таймеров-счетчиков. Режимы таймеров-счетчиков задаются с использованием регистра TMOD, а управление ими осуществляется при помощи ре гистра TCON. Для управления режимами энергопотребления микро-ЭВМ используется регистр PCON. Регистры IP и IE управляют работой системы прерываний микро-ЭВМ, а регистры SBUF и SCON - работой приемопередатчика последовательного порта. Описание таймеров-счетчиков, системы прерываний и приемопередатчика последовательного порта будет приведено ниже. ОРГАНИЗАЦИЯ ПОРТОВ ВВОДА/ВЫВОДА Все четыре порта 8051 - двунаправленные. Каждый из них содержит регистр-защелку (SFR Р0...РЗ), выходную цепь и входной буфер. Выходные цепи РО и Р2 вместе с входным буфером РО используются при обращении к внешней памяти. При этом на выходах РО младший байт адреса внешней памяти мультиплексируется с вводимым/ выводимым байтом. Выходы Р2 содержат старший байт адреса внешней памяти, если адрес 16-разрядный. При использовании 8-разрядного адреса на выводах Р2 присутствует информация из SFR Р2. Выводы порта РЗ помимо обычного ввода информации и вывода ее из SFR могут выполнять альтернативные функции. Описание этих функций приведено в табл. 3. Альтернативные функции могут быть активированы только если в соответствующие биты SFR порта РЗ предварительно занесены единицы. На рис. 3 приведены функциональные схемы регистров-защелок и буферов ввода/вывода каждого из четырех портов микро-ЭВМ. Каждый из битов регистра-защелки SFR является, по сути, D-тригге-ром, информация в который заносится с внутренней шины данных по сигналу запись в SFR Pi (i=0-3) от центрального процессорного элемента (CPU). С неинвертированного выхода D-триггера инфор- Альтернативные функции порта РЗ

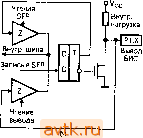

Чтение SFR Внутр. шина Запись в SFR ADR/DATA CNTR Чтение вывода Вывод БИС  ADR CNTR Чтение SFR Внутр. шина Замись Б SFR Внутр. нагрузка Чтение вывода Чтение SFR Аьтернатиеный сигнал (выходной) о Vcc Вывод БИС Внутр, шина Запись в SFR Аьтернативный Чтение сигнал (входной) вывода ЙВнутр. нагрузка Вывод БИС Рис. 3 мация может быть выведена на внутреннюю шину по сигналу чтение SFR Pi от CPU, а с вывода микросхемы ( из внешнего мира ) - по сигналу чтение выводов Pi . Одни команды активируют сигнал чтение SFR Pi , другие - чтение выводов Pi . Подробнее об этом будет сказано ниже. Как следует из рис. 3, выходные цепи РО и Р2 коммутируются сигналами CNTR , что обеспечивает вывод адресной информации и дан- 1 2 3 4 5 ... 20 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2004-2025 AVTK.RU. Поддержка сайта: +7 495 7950139 в тональном режиме 271761

Копирование материалов разрешено при условии активной ссылки. |